Advanced SRAM Array Design: Leakage Management and Vt Matching in FDSOI Technology

This document explores the intricate design of SRAM arrays utilizing FDSOI technology, focusing on minimizing leakage and enhancing Vt matching. We present a detailed block diagram of the thin chip architecture, including key macros such as Iread and NBTIsensor. We investigate the implications of the Yw buck converter and assess performance through the GG and ac top-level configurations. The study includes insights into the rwm series macros, specifically designed for fdsoi180, addressing challenges of memory performance in modern semiconductor applications.

Advanced SRAM Array Design: Leakage Management and Vt Matching in FDSOI Technology

E N D

Presentation Transcript

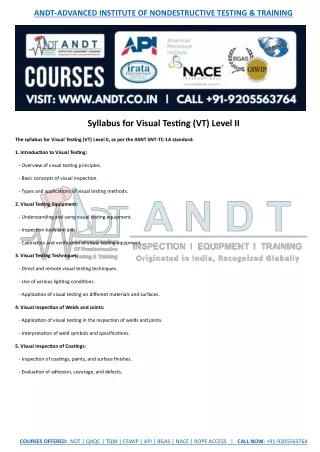

SRAM Array leakage FDSOI Vt matching SRAM Bfly & Iread macros

Thin Chip block diagram Yw_buck_final GG_top ac_topLevelNBTIsensor jfb_adc Kc_inv_chain rwm_alm_macro_fdsoi180 rwm_vtmm_macro_fdsoi180 rwm_bfly_macro_fdsoi180