Cours 4

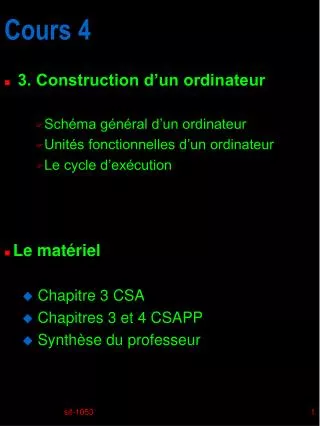

Cours 4. 3. Construction d’un ordinateur Schéma général d’un ordinateur Unités fonctionnelles d’un ordinateur Le cycle d’exécution Le matériel Chapitre 3 CSA Chapitres 3 et 4 CSAPP Synthèse du professeur. Introduction.

Cours 4

E N D

Presentation Transcript

Cours 4 • 3. Construction d’un ordinateur • Schéma général d’un ordinateur • Unités fonctionnelles d’un ordinateur • Le cycle d’exécution • Le matériel • Chapitre 3 CSA • Chapitres 3 et 4 CSAPP • Synthèse du professeur sif-1053

Introduction Tout ordinateur, gros ou petit, se compose au minimum d’une mémoire centrale (RAM) qui contient les programmes, les données et éventuellement les résultats, d’une unité centrale de traitement (UCT, CPU) qui exécute les programmes, d’unités d’entrées-sorties (I/O) permettant des échanges avec l’extérieur, et d’un bus de liaison qui permet l’interconnexion des trois modules précédents. sif-1053

Schéma général d’un ordinateur sif-1053

Schéma général d’un ordinateur sif-1053

Schéma général d’un ordinateur (Little Man Computer) sif-1053

Schéma général d’un ordinateur sif-1053

Schéma général d’un ordinateur sif-1053

Schéma général d’un ordinateur Registres importants: PC (program counter) ou IP (instruction pointer) IR (Instruction register) AX (Accumulator register) FR (flag register) sif-1053

Schéma général d’un ordinateur sif-1053

Unité arithmétique et logique (ALU) 0 1 1 sif-1053

CPU: PENTIUM sif-1053

CPU: PENTIUM PRO sif-1053

CPU: CORE DUO sif-1053

Schéma général d’un ordinateur L’information qui transite sur le bus de liaison se divise logiquement en trois catégories importantes bien distinctes: les données, que l’on définit comme tout ce qui est contenu dans la mémoire centrale; les adresses, qui permettent à l’unité centrale de lire ou d’écrire dans une position de mémoire particulière ou d’accéder à une unité périphérique quelconque; et enfin, divers signaux de commandes qui contrôlent le type et le synchronisme des échanges entre les différents composants. sif-1053

Schéma général d’un ordinateur Il est donc d’usage courant de représenter schématiquement le bus de liaison par trois bus spécialisés qui sont: le bus de données, le bus d’adresses et le bus de commandes. En pratique, les manufacturiers construisent généralement un seul bus physique qui intègre tous les signaux (données, adresses et commandes). sif-1053

Schéma général d’un ordinateur Chaque instruction exécutée par le CPU ne correspond pas à un seul événement, mais est constituée d’une séquence de phases distinctes appelées micro-cycles ou micro-opérations. Chacune de ces micro-opérations est cadencée par rapport à une horloge système Pour une horloge système de 1 GHz, chaque micro-opérations devrait durée au plus 1 nanoseconde t = 1/f , 1.0 = 1 X 10-9 s = 1 nsec 1 X 109 sif-1053

Schéma général d’un ordinateur Micro-opérations correspondant à l’exécution d’une instruction typique sif-1053

Bus de donnés: Typiquement de 32 bits de large mais de plus en plus à 64 bits Bus d’adresse: 32 bits de large mais sera aussi élargi bientôt Bus de commande: Environ 15 lignes responsables de l’aiguillage des tâches sif-1053

Bus du PENTIUM II: AGP (Accelerated Graphic Ports) et PCI (Peripheral Component Interface) sif-1053

Bus du PENTIUM IV (2002): AGP (Accelerated Graphic Ports) et PCI (Peripheral Component Interface) sif-1053

Bus du PENTIUM IV: PCI EXPRESS(Peripheral Component Interface) sif-1053

Bus (interconnexions typiques) sif-1053

Le rôle de la mémoire principale (RAM) Un programme doit être enregistré en mémoire avant le début de son exécution. La mémoire, à partir de laquelle le programme s’exécute, est appelée mémoire centrale ou mémoire principale (RAM). Cette mémoire contient d’une part, les instructions du programme que la machine doit exécuter; les données, souvent appelées opérandes, sur lesquelles la machine effectue les traitements dictés par les instructions; et enfin, les résultats qui sont les conséquences de l’exécution d’une ou de plusieurs instructions. sif-1053

Pour celui qui programme un ordinateur, la mémoire apparaît comme un ensemble de cases juxtaposées. Chaque case est désignée par un numéro (0, 1, 2,,, 65535, etc.), que l’on appelle adresse, et contient un mot. Ce contenu est un mot binaire d’une longueur donnée et fixe. S’il est de 8 bits, on le nomme octet (byte). Pour en faciliter la lecture (pour un humain), cet octet est représenté par deux chiffres hexadécimaux. Chaque octet peut représenter: une instruction du programme, ou une donnée, ou un résultat. sif-1053

Relation entre la largeur des adresses et la longueur de la mémoire sif-1053

Little-endian VS Big-endian: arrangement des octets en mémoire des mots de 16, 32, 64 bits Par exemple si nous déclarons les vecteurs suivants en langage C: unsigned char b1[ ] = {1, 2, 3, 4, 5, 6, 7, 8, 9 ,10, 252, 253, 254, 255 }; unsigned short b2[ ] = {1, 2, 3, 4, 5, 254, 255, 256, 257 , 65532, 65533, 65535, 65536 }; unsigned int b4[ ] = {1, 2, 3, 4, 5, 254, 255, 256, 4095 , 4096, 4097, 4294967295 }; sif-1053

Little-endian VS Big-endian INTEL VS MOTOROLA sif-1053

L’unité centrale de traitement doit “traiter” essentiellement deux types d’information: les instructions et les opérandes (données). L’UCT est divisée fonctionnellement en deux unités constituantes: l’unité de contrôle (UC), également appelée unité d’instructions ou unité de commande; et l’unité arithmétique et logique (UAL) ou unité de traitement. Le rôle de l’unité centrale sif-1053

Au cours d’un traitement, les différentes informations: instructions, données et résultats, doivent être temporairement conservées à l’intérieur de l’unité centrale dans des éléments de mémoire capables de contenir une information. Il s’agit tout simplement de cases de mémoire comparables à celles que l’on retrouve à l’intérieur de la mémoire principale (RAM), mais ces cases sont situées à l’intérieur de l’unité centrale et elles sont appelées registres. Exemples EAX: registre accumulateur de 32 bits AX: registre accumulateur de 16 bits sif-1053

Une unité centrale possède toujours un certain nombre de registres que l’on identifie par des noms particuliers. Par exemple, un registre par où transite les données ou les résultats s’appelle habituellement “registre accumulateur”, ou plus simplement accumulateur. L ’ensemble des registres et de l ’UAL forment ce que l ’on identifie comme « le chemin des données » (data path). sif-1053

Jusqu’à présent notre ordinateur exécute un programme initialement enregistré en mémoire centrale, portant sur des données également enregistrées en mémoire centrale, et les résultats sont rangés dans la mémoire au fur et à mesure de leur obtention. Les programmes et les données que l’on charge en mémoire centrale proviennent d’unités périphériques, par exemple un terminal ou un lecteur de disque. Il faut donc donner à la machine les moyens de communiquer avec l’extérieur, c’est-à-dire avec ses unités périphériques. C’est le rôle des unités d’entrées-sorties (I/O). Le rôle des unités d’entrées/sorties sif-1053

Il existe deux grandes catégories d’unités périphériques, tout d’abord les unités de communication (terminal, souris, imprimante) qui permettent le dialogue homme/machine. Et en second lieu les mémoires auxiliaires (disques, bandes magnétiques) dont les capacités de stockage (en nombre d’octets) sont supérieures à celle de la mémoire principale. sif-1053

Il existe également une autre catégorie d’unités de communication extrêmement importante, les unités qui permettent les communications machine/machine. On retrouve dans cette catégorie toutes les interfaces nécessaires au réseautage local ou étendu. sif-1053

PCI: Peripheral Component Interconnect ISA: Industry Standard Architecture sif-1053

Examinons comment l’ordinateur s’y prend pour résoudre un programme simple, tel l’addition des nombres 8 et 2. Algorithme 1) Le nombre 8 est placé dans le registre accumulateur; 2) ajouter 2 au contenu de l ’accumulateur; 3) recopier le contenu de l’accumulateur en mémoire centrale, afin de conserver le résultat de l’addition; 4) on s’arrête ici. Exécution d’un programme simple sif-1053

Remarquer que l’on a délibérément choisi de ne pas transmettre le résultat de l’addition au monde extérieur (à un terminal par exemple), question d’avoir un programme simple. On se contente de conserver le résultat de l’addition en mémoire principale. sif-1053

La seconde étape consiste à traduire notre algorithme selon un ensemble d’instructions un peu plus près de ce que peut comprendre un ordinateur. Pour ce faire, les manufacturiers d’ordinateurs offrent tous un langage symbolique qui nous permet de représenter notre algorithme sous une forme beaucoup plus compacte, et beaucoup plus près de ce que la machine peut comprendre. Par exemple, notre algorithme pourrait correspondre au langage symbolique suivant: sif-1053

1) MVI A, 8 // A <- 8 2) ADI A, 2 // A <- A + 2 3) STA 2FFF // 2FFF <- A 4) HLT sif-1053

1) MVI A correspond au code 3E 2) ADI A correspond au code C6 3) STA correspond au code C9 4) HLT correspond au code 76 sif-1053

Il ne nous reste plus qu’à assembler (recopier) les instructions de notre programme, en utilisant les codes numériques et en y ajoutant les opérandes que l’on code également sous forme hexadécimale. Ce qui nous donne: 1) 3E 8 2) C6 2 3) C9 2FFF 4) 76 sif-1053

Chez tous les ordinateurs, l’exécution d’une instruction par l’UCT suit un processus bien déterminé. Ce processus porte le nom de “cycle d’extraction, de décodage et d’exécution” ou tout simplement cycle extraction-décodage-exécution (en anglais, FETCH-DECODE-EXECUTE cycle). Certains auteurs l’appellent également FETCH-EXECUTE sif-1053

Little Man Computer sif-1053

FETCH (LOAD) sif-1053