Efficient Model Checking of Software Product Lines Using Featured Transition Systems

70 likes | 187 Vues

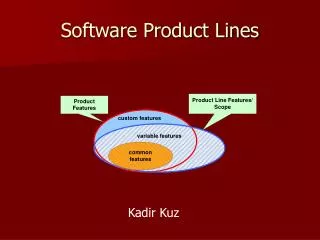

This paper discusses advancements in model checking within software product lines (SPLs) through the use of Featured Transition Systems (FTS). It highlights key works presented at ICSE conferences, including techniques for efficient verification of temporal properties using Linear Temporal Logic (LTL). The relationship between different studies showcases improvements in symbolic model checking and simulation-based abstraction methods. By leveraging FTS, the verification process becomes more streamlined, allowing checks on the entire product line rather than individual products, thus enhancing efficiency and reducing problem space.

Efficient Model Checking of Software Product Lines Using Featured Transition Systems

E N D

Presentation Transcript

Model Checking Behaviors of Software Product Lines Using Featured Transition Systems (FTS)

Source Papers • A. Classen, P. Heymans, P.-Y. Schobbens, A. Legay, and J.-F. Raskin, “Model checking lots of systems: efficient verification of temporal properties in software product lines,” ICSE ’10. • A. Classen, P. Heymans, P.-Y. Schobbens, and A. Legay, “Symbolic model checking of software product lines,” ICSE ’11 • M. Cordy, A. Classen et al. “Simulation-based Abstraction for Software Product Line Model Checking,” ICSE ‘12

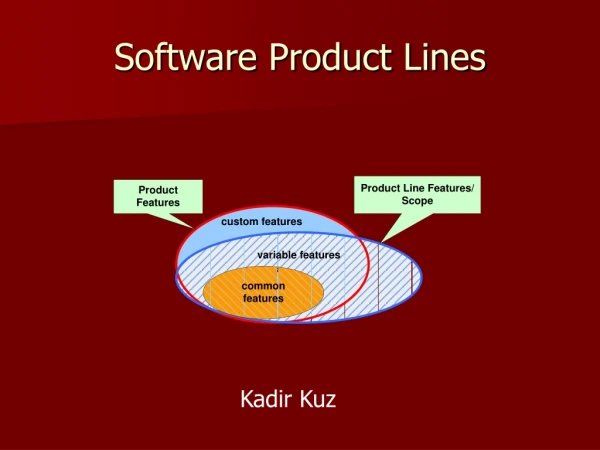

Relations between The Papers • ICSE’ 10: Concept and Model Checking of Featured Transition Systems (LTL: Linear Temporal Logics) • ICSE’ 11: A faster LTL Solver • ICSE’ 12: Reduce Problem Space (States in FTS)

FM + TS = FTS Priority: Child > Parent

Benefits of FTS • Without FTS • Check behaviors of products one by one • With FTS • Check as a whole (based on TS checking techniques, e.g. Linear Temporal Logics)