Venus: A Reliable & Reconfigurable Satellite Computer

90 likes | 176 Vues

טכניון – מכון טכנולוגי לישראל הפקולטה להנדסת חשמל. Venus: A Reliable & Reconfigurable Satellite Computer. Students: Guy Derry Gil Wiechman Instructor: Isaschar Walter In cooperation with MOD Winter-Spring 2003. 1 According to publications by NASA & CCSDS. Abstract.

Venus: A Reliable & Reconfigurable Satellite Computer

E N D

Presentation Transcript

טכניון – מכון טכנולוגי לישראל הפקולטה להנדסת חשמל Venus: A Reliable & Reconfigurable Satellite Computer Students:Guy Derry Gil Wiechman Instructor:Isaschar Walter In cooperation with MOD Winter-Spring 2003

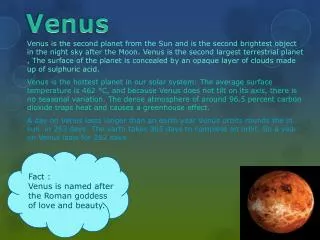

1 According to publications by NASA & CCSDS Abstract • Satellite computer systems must meet various demands • Endurance to cosmic radiation1 • Power consumption limitations • Weight limitations • Space systems demand reliability • Radiation significantly reduced components’ MTBF • Repair is not an option… • The approach – Redundancy • Data traffic monitoring • Data storage monitoring

System Description • The satellite computer is implemented on a Xilinx Virtex2Pro FPGA as a fully operational PC system containing: • PPC405 RISC Processor • External SDRAM Module • Internal BRAM Module (containing the application) • UART16550 Serial Communication Module incl. TMR Units • Autonomous Bus Testing Mechanism • Space-Weather-Simulation Unit (for system testing)

System Description The processor runs a typical application consisting mainly of memory-read-write operations and serial communication, which simulate the satellite computer’s missions in space. The TMR module corrects errors occurring in the serial channel, and the bus tester unit monitors the correct startup of the system, and the correct operation of the system bus. Several types of errors can be injected into the system (via DIP switches), and the correct operation of the system can be viewed via a HyperTerminal host and the LED array located on the development board.

System Bus System Block Diagram Memory module Memory EDAC Memory EDAC Memory EDAC Processor module Peripheral module Processor Processor Peripheral Processor Peripheral Peripheral Monitor module Monitor Monitor Monitor

Hardware Xilinx Virtex2Pro Development Board Serial Communications Cable SDRAM Module Software HyperTerminal Communication Host PPC405 Testing Application wrote 1300 and 1174 read 1300 and 1174 wrote 1089 and 1191 read 1089 and 1191 wrote 521 and 58 read 521 and 58 wrote 733 and 330 read 733 and 330 wrote 1310 and 217 read 1310 and 217 wrote 1179 and 966 read 1179 and 966 wrote 0 and 359 read 0 and 359 wrote 37 and 333 read 37 and 333 Specification

FPGA Block Diagram (Not implemented) I/O TMR I/O TMR Memory EDAC Processor (PPC405) System Bus Bus Tester (slave) Bus Tester (slave) Bus Tester (master) Bus Tester (master)

TMR Module - Implementation I/O TMR Module PLB UART PLB PLB UART TMR Monitor TMR Monitor I/O Interface PLB UART SWS

User Reset Reset Timing Unit System Reset Tester Reset Reset Timing Unit System Bus Bus Tester (slave) Bus Tester (master) Set Dog Watchdog Bark Tester Reset Request Odd Bus Fail Even Bus Tester - Implementation LED array