11 slides 10 .0 3 .2010

120 likes | 271 Vues

SVD Finesse Transmitter Board (FTB) (Sender Part for HSD Link). 11 slides 10 .0 3 .2010. Version 5 , after: E-mail from Markus Friedl ( 05 .0 3 ). 10 .0 3 .2010 wacek ostrowicz . SVD Finesse Transmitter Board (FTB) (Sender Part for HSD Link). One main conclusion:.

11 slides 10 .0 3 .2010

E N D

Presentation Transcript

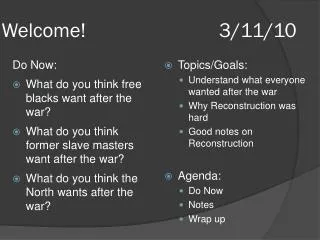

SVD Finesse Transmitter Board (FTB) (Sender Part for HSD Link) 11 slides10.03.2010 Version 5, after: E-mail from Markus Friedl (05.03) 10.03.2010 wacek ostrowicz

SVD Finesse Transmitter Board (FTB) (Sender Part for HSD Link) One main conclusion: Markus strongly needs the FADC-CDB( + FCRB) Now: FADC-CDB is renamed to SVD-CONTROLLER or in shorter version: SVDctlr 10.03.2010 wacek ostrowicz 1/11

Giessen Box(es) FADC#k from timing system SVD Finesse Transmitter Board (FTB) (Sender Part for HSD Link) Whom I may talk to ? Soeren Lange Mikihiko Nakao Liu Zhen-An opt opt HSD Link FTB#k Markus Friedl RJ45 Mikihiko Nakao FCRB SVDctlr RJ45 10.03.2010 wacek ostrowicz 2/11

SVD Finesse Transmitter Board (FTB) (Sender Part for HSD Link) CLK1... Clock & Trigger Distribution FADC#80 FTB#80 opt CLK1... FPGA opt SVDctlr RJ45 FADC#1 FTB#1 opt FPGA opt … RJ45 TTD FCRB RJ45 #80 CLK1 CLK2 TRG TAG[ ] IRST TRG ACK READY … … FPGA RJ45 #1 RJ45 RJ45 #81 10.03.2010 wacek ostrowicz 3/11

FADC#k SVDctlr opt opt FCRB FTB#k RJ45 RJ45 SVD Finesse Transmitter Board (FTB) (Sender Part for HSD Link) x 1 SVDctlr: SVD - CONTROLLER FCRB: Finesse Clock Receiver Board Slides: 6/11 – 8/11 x 80 Slides: 9/11 – 11/11 10.03.2010 wacek ostrowicz 4/11

+ + + + + + + - - - - - - - SVD Finesse Transmitter Board (FTB) (Sender Part for HSD Link) SVDctlr CLKs IRST … to FADC#k Connection between TTD and FCRB Signals between FCRBand SVDctlr Only one such set FCRB FPGA TRG TAG [ ] *Unified part* IRST Serial Link Manager Data IN Data Out Reserve TCLK GlobLastProcessedTrgNb [ ] from/to TTD RJ45 FADC Ready/Busy CLK1 Clock manager CLK2 10.03.2010 wacek ostrowicz 5/11

In fact it is NOT unified part!!! FIFO1 from/to FRB on COPPER RI/O core1 OpTr HSD Link *Unified part* Serial Link Manager Data IN Data Out Reserve TCLK from/to TTD Serial Link Manager Data IN Data Out Reserve TCLK RJ45 from/to TTD RJ45 Unified part Clock manager Clock manager And the signals ‘from/to TTD’ are slightly diffrent!!! 10.03.2010 wacek ostrowicz 6/11

SVD Finesse Transmitter Board (FTB) (Sender Part for HSD Link) Signals between SVDctlr and FCRB: SVDctlr <-- FCRB: CLK1 SVDctlr <-- FCRB: CLK2 SVDctlr <-- FCRB: TRG SVDctlr <-- FCRB: TAG[7:0] SVDctlr <-- FCRB: IRST SVDctlr--> FCRB: GlobalLastProcessedTriggerNumber [ ] SVDctlr --> FCRB: Ready/Busy It is still waiting for confirmation by Markus (what he needs) and Mikihiko (what he agrees with) ? Signals between TTD and FTB#k: TTD --> FTB: TCLK TTD --> FTB: Data In TTD <-- FTB: Data Out TTD ?? FTB: reserve 10.03.2010 wacek ostrowicz 7/11

SVD Finesse Transmitter Board (FTB) (Sender Part for HSD Link) Or direct to FADC-CDB…???: Connection and signals between TTD and FADC-CDB Only one such board FADC-CDB CLKs IRST … to FADC#k ? Markus, is it possible? FPGA TRG TAG [ ] Unified part IRST Serial Link Manager Data IN Data Out Reserve TCLK GlobLastProcessedTrgNb [ ] from/to TTD RJ45 FADC Ready/Busy CLK1 Clock manager CLK2 10.03.2010 wacek ostrowicz 8/11

+ + + + + + + - - - - - - - SVD Finesse Transmitter Board (FTB) (Sender Part for HSD Link) Connections to/from FTB#k Signals between FADC#k and FTB#k Signals between TTD and FTB#k For every k from 1 to 80 FADC#k ‘CLKs’ IRST … from FADC-CDB see next slides RI/O core2 to Pixel DRU XD[31:00] FTB fmw OpTr Opto-Link FIFO2 Link3 DA_EN DATA [ ] HEADER TRAILER FIFO1 Link2 from/to FRB on COPPER RI/O core1 DCLK OpTr HSD Link BSY_FTB REGs Link1 TRG FTB#k TAG[7:0] IRST Data IN Data Out Reserve TCLK from/to TTD Serial Link Manager LocLastProcessedTrgNb [ ] RJ45 DataProcessCompl FTB Ready/Busy Local FADC Ready/Busy Unified part SVD oriented firmware Pipeline clock Clock manager FPGA 10.03.2010 wacek ostrowicz 9/11

SVD Finesse Transmitter Board (FTB) (Sender Part for HSD Link) Signals between FADC#k and FTB#k: FADC --> FTB: XD[31:00] +/- FADC --> FTB: DA_EN +/- FADC --> FTB: HEADER +/- FADC --> FTB: TRAILER +/- FADC --> FTB: DCLK +/- {32MHz (42MHz as option)} FADC <-- FTB: BSY_FTB FADC --> FTB: Local FADC Ready/Busy Signals between TTD and FTB#k: TTD --> FTB: TCLK +/- TTD --> FTB: Data In +/- TTD <-- FTB: Data Out +/- TTD <-> FTB: reserve +/- Internal (in FPGA) signals between TTD (SLM)* and FTB fmw**: TTD (SLM) --> FTB fmw: SCK (pipeline clock) TTD (SLM) --> FTB fmw: TRG TTD (SLM) --> FTB fmw: TAG[7:0] TTD (SLM) --> FTB fmw: IRST TTD (SLM) <-- FTB fmw: LocalLastProcessedTriggerNumber [ ] TTD (SLM) <-- FTB fmw: DataProcessCompletion TTD (SLM) <-- FTB fmw: FTB Ready/Busy TTD (SLM) <-- FTB fmw: Local FADC Ready/Busy * TTD (SLM) – Serial Link Manager for TTD implemented in FPGA on FTB as ‘Unified Part’ ** FTB fmw – firmware implemented in FPGA on FTB as ‘SVD oriented Part’ 10.03.2010 wacek ostrowicz 10/11

SVD Finesse Transmitter Board (FTB) (Sender Part for HSD Link) Internal (in FPGA) signals between FTB fmw** and FIFO1 for HSD Link*** : FTB fmw --> FIFO1: FF[31:0] FTB fmw --> FIFO1: FWCLK (42MHz) FTB fmw --> FIFO1: FWENB L i n k 2 Remain internal (in FPGA) signals between RI/O core1 and FTB fmw**: RI/O Core1 --> FTB fmw: LA[6:0] RI/O Core1 <-> FTB fmw: LD[7:0] RI/O Core1 --> FTB fmw: LWR RI/O Core1 --> FTB fmw: CSB RI/O Core1 --> FTB fmw: FRST L i n k 1 Internal (in FPGA) signals between FTB fmw** and FIFO2 for Pixel DRU****: FTB fmw --> FIFO2: FF[31:0] FTB fmw --> FIFO2: FWCLK (42MHz) FTB fmw --> FIFO2: FWENB L i n k 3 ** FTB fmw – firmware implemented in FPGA on FTB as ‘SVD oriented Part’ *** FIFO1 for HSD Link – Pipeline retaining DATA waiting for sending through the HSD Link **** Pixel DRU – Pixel Data Reduction Unit 10.03.2010 wacek ostrowicz 11/11

![[0-11]](https://cdn1.slideserve.com/3481506/slide1-dt.jpg)

![[110-] [10-0] [1-00] [00-0] [11-0]](https://cdn2.slideserve.com/4741674/slide1-dt.jpg)