VHDL-kieli

VHDL-kieli. Standardoitujen kuvauskielten kytn perusteetRiippumattomuus piirivalmistajista. sama kuvaus voidaan toimittaa usealle eri piirivalmistajalle (ainakinperiaatteessa).Riippumattomuus suunnittelutykaluista. stardardimuotoinen tekstitiedosto voidaan helposti siirtsuunnitteluty

VHDL-kieli

E N D

Presentation Transcript

1. VHDL-kieli Johdanto

Laitteiston kuvauskieli eli HDL (Hardware Description Language) on tekstimuotoinen tapa kuvata digitaalipiiri tai �laite.

Valtaosa k�yt�nn�n digitaalipiirisuunnittelusta tehd��n kuvauskielell�.

K�ytet��n erityisesti kuvattaessa asiakaskohtaisia digitaalipiirej� ja ohjelmoitavia logiikkaverkkoja.

Kuvauskielet muistuttavat ohjelmointikieli�.

� laitteistossa on sek� rinnakkaista ett� per�kk�ist� toimintaa.

� ohjelmistossa on yleens� vain per�kk�ist� toimintaa.

Kuvauksia voidaan k�ytt�� simulointiin, piirisynteesiin ja testaukseen.

2. VHDL-kieli Standardoitujen kuvauskielten k�yt�n perusteet

Riippumattomuus piirivalmistajista.

� sama kuvaus voidaan toimittaa usealle eri piirivalmistajalle (ainakin

periaatteessa).

Riippumattomuus suunnitteluty�kaluista.

� stardardimuotoinen tekstitiedosto voidaan helposti siirt��

suunnitteluty�kalusta toiseen.

Hyv�t valmislohkojen (IP Blocks) k�ytt�mahdollisuudet.

� laitevalmistajan omat valmislohkot.

� piirivalmistajan valmislohkot.

� ty�kalutoimittajan valmislohkot.

� erikseen ostetut (third party) valmislohkot.

� valmislohkojen k�ytt� lyhent�� usein suunnitteluaikaa paljonkin.

3. VHDL-kieli VHDL = VHSIC Hardware Description Language

� VHSIC = Very High Speed Integrated Circuit (USA:n DoD:n hanke)

Alkuper�inen versio IEEE 1076-1987 vuonna 1987

P�ivitys versioksi IEEE 1076-1993 vuonna 1993

Kehitysty� jatkuu

Hyvin rikas ja monipuolinen kieli

My�s laaja ja osin mutkikaskin

Sujuva k�ytt� vaatii sek� opiskelua ett� erityisesti k�yt�nn�n kokemusta

Kuvattua laitetta tai piiri� nimitet��n suunnitteluyksik�ksi (entity)

Suunnitteluyksik�ill� on hierarkia

ylemm�n tason suunnitteluyksikk� koostuu alemman tason

suunnitteluyksik�ist� eli moduuleista

samaa moduulia voidaan k�ytt�� useita kertoja

4. VHDL-kieli VHDL-suunnittelussa on tavoitteena saada aikaan VHDL-malli.

VHDL-kieli on t�ysin simuloituvaa, mutta ei t�ysin syntesoituvaa.

-osaa kielen rakenteista ei pystyt� toteuttamaan piiritasolla.

Malli voi kuvata:

- VHDL-komponenttia,

- kokonaista ASIC/FPGA piiri�,

- piirikorttia

- tai korttien muodostamaa j�rjestelm��,

- tai se voi olla niin sanottu testipenkki.

VHDL-malli on teksti� (merkkijono), joka kirjoitetaan

tekstink�sittelyohjelman avulla.

5. VHDL-kieli VHDL-mallin rakenne

1. Entity Declaration (primary) Suunnitteluyksik�n esittely

2. Package Declaration (primary) Kokoelman esittely

3. Configuration Declaration (p) Kokoonpanon esittely

4. Architecture (secondary) VHDL-arkkitehtuuri

5. Package Body (secondary) Kokelman ydin.

Entity Declaration on kirjastoyksikk�, jossa m��ritell��n mallinnetun logiikan liittyminen ymp�rist��ns�, liittimen kuvaus

Architecture on kirjastoyksikk�, jossa m��ritell��n varsinainen mallinnettava logiikka

Design Unit = Entity + Architecture on kokonaisuus, jota voidaan simuloida.

6. VHDL-kieli Yksinkertaisin malli

Mallissa on Entity + Architecture

= yksi suunnitteluyksikk�

Simuloitava VHDL-malli voidaan aina

esitt�� t�ss� muodossa.

Esim. AND-portti

VHDL-kielell�.

7. VHDL-kieli Esim. Nand-portti.

ENTITY nand2 IS

PORT (

a: IN BIT;

b: IN BIT;

f: OUT BIT);

END nand2;

ARCHITECTURE behavior OF nand2 IS

BEGIN

f <= a NAND b;

END behavior;

8. VHDL-kieli Kommentti, varattu sana ja tunniste

Kommentti (COMMENT)

� rivi tai rivin osa, joka alkaa -- (kaksi tavuviivaa) on kommentti

-- Ulkoisten tulosignaalien esittely

PORT (in1, in2, clk, reset): IN BIT; -- kaikkien tulosignaalien tyyppi BIT

Varattu sana ja tunniste

Avainsanat (keyword) ja operaattorit (operator) ovat varattuja sanoja

tunnisteet (identifier) ovat k�ytt�j�n antamia nimi�.

Alkavat kirjaimella, sallittuja merkkej� englannin kirjaimet, numerot ja _

_ ei saa olla viimeinen merkki eik� niit� saa olla kahta per�kk�in

isoja ja pieni� kirjaimia ei erotella: IN1 = in1 = In1

PORT, IN, NAND ovat varattuja sanoja

in1, nand2, toiminta ovat tunnisteita

9. VHDL-kieli Varatut sanat:

abs access after alias all and architecture array assert attribute begin block body buffer bus case component configuration constant disconnect downto else elsif end entity exit file for function generate generic guarded if impure in inertial inout is label library linkage literal loop map mod nand new next nor not null of on open or others out package port postponed process pure range record register reject rem report return rol ror select severity shared signal sla sll sra srl subtype then to transport type unaffected units until use variable wait when while with xnor xor

10. VHDL-kieli Objekti

Objekteja ovat portit, signaalit, muuttujat ja vakiot.

Portti (PORT) on suunnitteluyksik�n tulo- tai l�ht�signaali.

Signaali (SIGNAL) on suunnitteluyksik�n sis�inen signaali.

PORT (in1, in2, clk, reset: IN BIT; -- tulosignaalit

outa, outb, outc: OUT BIT); -- l�ht�signaalit

SIGNAL sis1, sis2, sis3: BIT; -- sis�iset signaalit

Muuttuja (VARIABLE) on VHDL-kuvauksen sis�inen objekti

VARIABLE p, q, sum: INTEGER; -- kolme kokonaislukumuuttujaa

Vakio (CONSTANT) on nimetty objekti, jolle on annettu vakioarvo

CONSTANT arvo0: STRING := "00"; -- vakion arvo0 arvo on jono "00"

11. VHDL-kieli Tyyppi

Tyyppi (TYPE) m��rittelee objektin (esimerkiksi signaalin tai muuttujan) arvot

VHDL-kielen keskeisi� tyyppej�

12. VHDL-kieli Bittijonon pituus ja kokonaisluvun arvoalue

Bittijonon bittien lukum��r� ja numerointi

BIT_VECTOR (1 TO 8); -- 8-bittinen bittijono, bitit 1�8

BIT_VECTOR (8 DOWNTO 1); -- 8-bittinen bittijono, bitit 8�1

Yksitt�iseen bittiin viitataan sen numerolla eli indeksill�

SIGNAL bj: BIT_VECTOR (8 DOWNTO 1); -- 8-bittinen bittijono bj

bj(8) <= '0'; bj(1) <= '1'; -- sijoitetaan 1. bitille arvo '0' ja 8. bitille '1�

Kokonaisluvun arvoalue esitet��n antamalla sen rajat

INTEGER RANGE 0 TO 255; -- etumerkit�n 8-bittinen luku

INTEGER RANGE 127 DOWNTO -128; -- 2:n kompl.-muot. 8-bittinen luku

13. VHDL-kieli Enumeroitu tyyppi ja operaattori

Enumeroitu tyyppi on k�ytt�j�n itse m��rittelem� tyyppi

arvot tunnisteita, merkkej� tai merkkijonoja

k�ytet��n esimerkiksi sekvenssipiirien toiminnallisissa kuvauksissa

tilojen m��rittelyyn

-- Nelitilaisen sekvenssipiirin tilat ovat alku, vali1, vali2 ja loppu

TYPE tilatyyppi IS (alku, vali1, vali2, loppu);

� Operaattori (operator)

� loogiset operaattorit AND, OR, NOT, NAND, NOR, XOR, XNOR

� aritmeettiset operaattorit +, -, *, /, **, MOD, REM, ABS

� vertailuoperaattorit =, /=, <, >, <=, >=

� ketjutusoperaattori &

� operaatioiden j�rjestys osittain m��ritelty: tarvittaessa k�ytet��n sulkuja

� loogisissa operaatioissa NOT ensin, AND ja OR samanarvoisia

14. VHDL-kieli Sijoituslauseet 1

Signaalin sijoituslauseella (signal assignment statement) sijoitetaan arvo signaalille tai portille

Sijoituslauseita on kolme erilaista: yht�aikainen, ehdollinen ja valikoiva

� Yht�aikainen (concurrent) signaalin sijoituslause

a <= '1'; -- sijoitetaan signaalille a vakioarvo 1

f <= a OR (b AND c); -- sijoitetaan signaalin f arvoksi lausekkeen arvo

� Ehdollinen (conditional) signaalin sijoituslause

f <= '0' WHEN a = '0' AND b = '0' ELSE -- 0, kun a = b = 0

c WHEN a = '0' AND b = '1' ELSE -- c, kun a = 0 ja b = 1

NOT c WHEN a = '1' AND b = '0' ELSE -- EI c, kun a = 1 ja b = 0

'1'; -- 1 muutoin

15. VHDL-kieli Sijoituslauseet 2

� Valikoiva (selected) signaalin sijoituslause

WITH ab SELECT

f <= '0' WHEN "00", -- 0, kun bittijono ab = 00

c WHEN "01", -- c, kun bittijono ab = 01

NOT c WHEN "10", -- EI c, kun bittijono ab = 10

'1' WHEN OTHERS; -- 1 muutoin

� Usea samaan sijoitukseen johtava ehto voidaan esitt�� yhdistettyin�

� k�ytet��n mm. Mooren koneen l�ht�signaalien sijoituksessa

WITH tila SELECT

f <= '1' WHEN alku | loppu, -- f = 1 tiloissa alku ja loppu

'0' WHEN OTHERS; -- f = 0 kaikissa muissa tiloissa

16. VHDL-kieli Ehdollinen ohjaus: IF- ja CASE-lauseet

17. VHDL-kieli Attribuutti

� Attribuutti (attribute) eli lis�m��re

� liitet��n objektiin ja ilmaisee sen ominaisuuden arvon

� muoto objekti'ATTRIBUTE

� valmiina yli kolmekymment�, k�ytt�j� voi m��ritell� omia

� synkronisissa sekvenssipiireiss� t�rke� attribuutti on 'EVENT

� k�ytet��n kellosignaalin muutoksen havaitsemiseen

-- Nousevalla reunalla liipaistavan D-kiikun tilanmuutoksen kuvaus

IF clk'EVENT AND clk = '1' THEN -- kellosignaalin nouseva reuna

q <= d; -- q:n arvoksi d:n arvo

END IF;

18. VHDL-kieli Prosessi (process)

� Her�tesignaalin muutoksen j�lkeen tapahtuvat tapahtumat

PROCESS (clk) -- D-kiikku kuvataan prosessina

BEGIN

IF clk'EVENT AND clk = '1' THEN -- kellosign. nouseva reuna

q <= d; -- kiikun tilaksi d-tulon arvo

END IF;

END PROCESS;

� Ajallisesti per�kk�iset tapahtumat (testipenkin kuvaus)

PROCESS -- testataan 2-tuloinen portti

BEGIN

a <= '0'; b <= '0'; WAIT FOR 100 NS; -- 1. her�te, odotet. 100 ns

a <= '0'; b <= '1'; WAIT FOR 100 NS; -- 2. her�te, odotet. 100 ns

a <= '1'; b <= '0'; WAIT FOR 100 NS; -- 3. her�te, odotet. 100 ns

a <= '1'; b <= '1'; WAIT; -- 4. her�te, pys�ytet��n

END PROCESS;

19. VHDL-kieli Yksinkertainen esimerkki prosessista:

Com_XOR: process (b,c)

begin

a<= b xor c;

end process;

- Com_XOR on prosessin nimi

- Sana process aloittaa prosessin m��rittelyn

(b,c) on ns. sensitivity list. T�m� tarkoittaa, ett� jos b:ss� tai c:ss� tapahtuu muutoksia, niin l�ht� a arvioidaan uudelleen. Sulkujen sis�ll� olevat signaalit kertovat mink� signaalien muutosten j�lkeen uudelleen arviointi tehd��n. Uudelleen arviointi tehd��n siten, ett� jokainen toiminto sanojen begin ja end v�lill� tehd��n uudelleen.

Prosessi on vain kuvaus siit�, mit� tulisi tapahtua lohkon sis�ll�.

20. VHDL-kieli Signaalin attribuutit

s�EVENT palauttaa tosiarvon (true) kun tapahtuma tapahtuu

s�STABLE: palauttaa tosiarvon kun signaalissa ei ole tapahtunut tapahtumaa

s�ACTIVE: palauttaa tosiarvon jos s=�1�

s�QUIET <time>palauttaa tosiarvon jos signaalissa ei ole tapahtunut mit��n ajan time aikana

s�LAST_EVENT palauttaa ajan edellisest� tapahtumasta

s�LAST_ACTIVE: palauttaa ajan edellisest� kerrasta kun s=�1�

s�LAST_VALUE: palauttaa s:n tapahtumaa edelt�neen arvon

21. VHDL-kieli Komponentti ja komponentin asennus

� Komponentti (component)

� komponenttim��rittely� k�ytet��n rakennekuvauksessa

� erikseen kuvattu suunnitteluyksikk� esitell��n komponenttina

COMPONENT and2

PORT (a, b: IN BIT; f: OUT BIT);

END COMPONENT

� Komponentin asennus (component instantiation)

� esitellyn komponentin ilmentym� kytket��n suunnitteluyksik�n

signaaleihin

� komponenttia voidaan k�ytt�� monta kertaa eri paikoissa

eka_and2: and2 PORT MAP (a => a1, b => b1, f => f1);

toka_and2: and2 PORT MAP (a => a2, b => b2, f => f2);

22. VHDL-kieli Esimerkki signaalin attribuuteista

IF (clk'EVENT AND clk='1')

IF (NOT clk'STABLE AND clk='1')

WAIT UNTIL (clk'EVENT AND clk='1');

IF RISING_EDGE(clk)

Kaikki yll� olevat ovat samalla tavalla syntesoituvia koodeja. (Eli odottavat kellon nousevaa reunaa.)

23. VHDL-kieli Suunnitteluyksik�n esittely p��lohkokaaviosta

Laitteen tai piirin p��lohkokaavio kuvautuu suunnitteluyksik�n esittelyksi:

24. VHDL-kieli

25. VHDL-kieli VHDL-k�ytt�ytymiskuvaus totuustaulusta

ENTITY muistutin IS

PORT (

cold, rain, onmat: IN BIT;

coat, umbr: OUT BIT);

END muistutin;

ARCHITECTURE tottaulu OF muistutin IS

BEGIN

coat <= '1' WHEN cold = '1' AND rain = '0' AND onmat = '1' ELSE

'1' WHEN cold = '1' AND rain = '1' AND onmat = '1' ELSE '0';

umbr <= '1' WHEN cold = '0' AND rain = '1' AND onmat = '1' ELSE '0';

END tottaulu;

26. VHDL-kieli VHDL-k�ytt�ytymiskuvaus lausekkeista

ENTITY muistutin IS

PORT (

cold, rain, onmat: IN BIT;

coat, umbr: OUT BIT);

END muistutin;

ARCHITECTURE lauseke OF muistutin IS

BEGIN

coat <= cold AND onmat;

umbr <= NOT cold AND rain AND onmat;

END lauseke;

27. VHDL-kieli

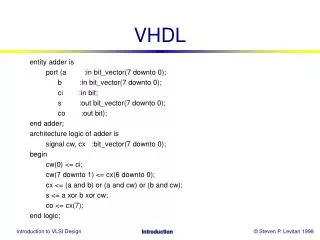

28. VHDL-kieli ENTITY

- Kaikki I/O-rajapinnan pinnien m��rittelyt

- MODE

- in, out, inout, buffer

- TYPE

- bit, std_logic, integer, �

29. VHDL-kieli SEKVENSSIPIIRIT

� Sekvenssipiirin l�ht�signaalien arvot riippuvat piirin tilasta

� piirin alkutilasta

� tulosignaalien historiasta

L�ht�signaalien arvot voivat riippua my�s tulosignaaleiden nykyisist� arvoista

� Sekvenssipiiri tallettaa ja muistaa oman tilansa

�� Sekvenssipiiriss� on sis�isi� takaisinkytkent�j�

�Kaksi p��tyyppi�:

� asynkroniset sekvenssipiirit

� synkroniset sekvenssipiirit

Asynkroninen sekvenssipiiri vaihtaa tilaansa tulosignaalin muuttuessa

Synkroninen sekvenssipiiri vaihtaa tilaansa erityisen tulosignaalin -

kellosignaalin - tahdissa

30. VHDL-kieli SR-salpa

� SR-salpa (S = Set, R = Reset) on yksinkertaisin sekvenssipiiri

� Se voidaan toteuttaa joko TAI-EI-porteilla (SR-salpa) tai

JA-EI-porteilla

� SR-salpa asetetaan S-tulolla ja nollataan R-tulolla

� Tulosignaaliyhdistelm� S = R = 1 on kielletty

entity srlatch is

Port ( s : in STD_LOGIC;

r : in STD_LOGIC;

q : buffer STD_LOGIC;

qnot : buffer STD_LOGIC);

end srlatch;

architecture Behavioral of srlatch is

begin

q <= '0' when r = '1' else

'1' when s = '1' else

q;

qnot <= '1' when r = '1' else

'0' when s = '1' else

qnot;

end Behavioral;

31. VHDL-kieli Kellotulolla varustettu D-kiikku

entity dkiikku is

port ( d : in STD_LOGIC;

clk : in STD_LOGIC;

q : out STD_LOGIC);

end dkiikku;

architecture Behavioral of dkiikku is

begin

p0: process (clk) is

begin

if (clk = '1') then

q <= d;

end if;

end process p0;

end Behavioral;

32. VHDL-kieli D-kiikku resetill� ja setill�.

ENTITY dff_asynch IS

PORT( D, Clk, Clr, Pre : IN STD_LOGIC;

Q, Qbar : OUT STD_LOGIC);

END dff_asynch;

ARCHITECTURE behavioral OF dff_asynch IS

BEGIN

PROCESS(D, Clk, Clr, Pre)

BEGIN

IF Clr = '0' THEN -- Don�t wait for clock

Q <= '0';

Qbar <= '1';

ELSIF Pre = '0' THEN

Q <= '1';

Qbar <= '0';

ELSIF (Clk'event) AND (Clk='1') THEN -- Positive Edge

Q <= D;

Qbar <= not D;

END IF;

END PROCESS;

END behavioral;

33. VHDL-kieli Laskuri

entity counter is

generic(n: natural :=2);

port( clock: in std_logic;

clear: in std_logic;

count: in std_logic;

Q: out std_logic_vector(n-1 downto 0) );

end counter;

architecture behv of counter is

signal Pre_Q: std_logic_vector(n-1 downto 0);

begin -- behavior describe the counter

process(clock, count, clear)

begin

if clear = '1' then Pre_Q <= Pre_Q - Pre_Q;

elsif (clock='1' and clock'event) then

if count = '1' then Pre_Q <= Pre_Q + 1;

end if;

end if;

end process;

Q <= Pre_Q;

end behv;