General-Purpose Computer Design: Enhancements From Game of Life Example

This document discusses the development of a general-purpose computer architecture, specifically addressing issues found in a previous implementation. Key problems include the use of extensive ROM, variable storage in registers, and limitations in space. Solutions involve defining more adaptable instructions and shifting variable storage from registers to RAM. It further explores the structure of instructions, control operations, and the components of the circuit necessary for efficient processing. Examples include arithmetic and logic operations, along with memory-related instructions and control flow management.

General-Purpose Computer Design: Enhancements From Game of Life Example

E N D

Presentation Transcript

Toward a general purpose computer II Example: Game of Life

Problems in the previous implementation • Similar instructions in different parts of the algorithm require different lines Very large ROM

Example N = N+1 tmp = i+1 Target = A + B

Problems in the previous implementation • All the variables of the algorithm are stored in registers. 1. Change in the algorithm will require change in hardware 2. Registers are expansive. 3. There is limited space.

Solution to 1 (and 2) • Define more general instructions • The algorithm will be a set of the general instructions.

List of instruction in game of life Register no. 2 • $3 = $1 + $2 • $3 = $1 – $2 • $3 = And($1,$2) • $3 = OR($1,$2) • $3 = Decode($1) • $3 = set on less $1,$2 • $1 = VAL

The set on less instruction • $3 = set on less $1,$2 • $3 = 00000…01 if $1 < $2 • $3 = 00000…00 otherwise.

Solution to 2 • Move the variables to the RAM We will need instructions to load and store registers in the RAM

Load and Store instructions • Load addr,$1 – load address into $1 • Store addr , $1 – store $1 into addr

Instruction control • Goto the next instruction • j Addr • Jump to instruction in address addr

Control the PC branching 1 2 3 4

Control the PC branching • PC = PC+1 • Check xxx happenedIf it didn’t PC = 4 • IR PC 1 2 3 4

PC control • Jne $1,$2,Addr • If $1 ≠ $2 Goto Addr • Je $1,$2,Addr • If $1 = $2 Goto Addr

The instructions in the system • $3 = $1 + $2 • $3 = $1 – $2 • $3 = And($1,$2) • $3 = OR($1,$2) • $3 = Decode($1) • $3 = set-on- less($1,$2) • $1 = VAL Arithmetic/Logic operations Memory related operations Control operations • j Addr • Jne $1,$2,Addr • Je $1,$2,Addr • Load addr,$1 • Store addr,$1 Instruction

Assumptions: • We have 16 registers $1…$26 ($0 is always zero). • The RAM has 65536 entries of 16bits (16bit address) • The program ROM has 65536 entriesof 32bits each.

The structure of instructionsArithmetic logic Total 16 registers [13-16] [0-4]First 5 bits reserved [5-8] [9-12]

The structure of instructions$1 = VAL [0-4]First 5 bits reserved [5-8] [9-24]

The structure of instructionsMemory instruction load/store addr,$1 [0-4] [5-8] [9-24]

The structure of instructionsControl instructions j/jne/je $1,$2,Addr [0-4] [5-8] [9-12] [13-28]

Note about the control instructions • In the j instruction we ignore the first and second fields.

The components of the circuit:The ALU Operand B Operand A ALU Operation Code Is zero(1 bit) Result

The components of the circuit:The Registers Registers Data 1 Address Data 1 Data 2 Address Data 2 WriteAddress Write Data Write

The components of the circuit:The RAM Read Note 1: The RAM is the one you saw in class without the MAR and MBR Note 2: The RAM is implemented with Latches! RAM Read Address Data 1 WriteAddress Write Data Write

The components of the circuit:The PC and the program • PC – holds the next address • IR - holds the current instruction Program ROM IR PC Write Write

A note before implementation • Several time cycles were lost because not all instructions have the same number of steps. Solution: Use a counter for the micro-instructions. CAR

The components of the circuit:CAR, example with arithmetic instruction CAR = 0: IRPC, PC=PC+1, CAR=CAR++ CAR = 1: Perform the code CAR = 0 Goto the next instruction

The components of the circuit:CAR, example with jne $1,$2,Addr CAR = 0: IRPC, PC=PC+1, CAR=CAR++ CAR = 1: $1-$2, if not zero PCAddr CAR = 0 Goto the next instruction

The components of the circuit:CAR, example with arithmetic instruction CAR = 0: IRPC, PC=PC+1, CAR=CAR++ CAR = 1: Perform the code Goto the next instruction For efficiency, we will NOT use the ALU here.

The CAR circuit 1 Adder CAR C1 MUX 000

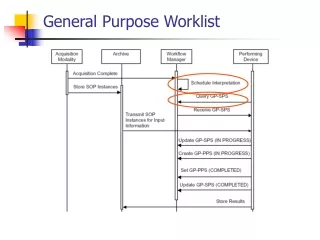

Program ROM IR PC 3 [BITS 13-28] [BITS 5-8] 16Registers [BITS 9-12] 1 [BITS 5-8] 5 2 [BITS 13-16] 4 [BITS 9-24] [BITS 5-8] RAM 1 ALU [BITS 9-24]

Mirco-instructions CAR Program ROM IR [BITS 0-4] PC 3 All the control in the system [BITS 13-28] [BITS 5-8] 16Registers [BITS 9-12] 0 1 1 [BITS 5-8] 5 1 0 1 2 [BITS 13-16] 0 4 [BITS 9-24] 2 [BITS 5-8] RAM 1 1 ALU 0 [BITS 9-24]

Mux3 CAR Program ROM IR PC 3 CAR control PCload IRload Mux2 Mux5 16Registers 1 Read 5 2 Mux4 4 RAM ALUop 1 ALU Write Mux1 Write

The micro-instruction ROMExample: CAR = 0: IRPC, PC=PC+1, CAR=CAR++ CAR = 1: $3=$2+$1 CAR = 0

The micro-instruction ROMExample: We don’t care about these CAR = 0: IRPC, PC=PC+1, CAR=CAR++ CAR = 1: $3=$2+$1 CAR = 0 The meaning is: Put in PC the result Of PC+1

The micro-instruction ROMExample: CAR = 0: IRPC, PC=PC+1, CAR=CAR++ CAR = 1: $3=$2+$1 CAR = 0

In addition • In order to implement the jne instruction we need a conditional write on the PC. • The essence is in here

Addition to the ROM: 1-bit flags that are used in the jne,je

Mirco-instructions Program ROM IR PC PC write Branch equal Branch not equal ALU Zero status bit

The program ROM Instruction type 00 Instruction sub type Reg3 Reg1 Reg2

Saving more space • The fetch is divided into 2 cycles • Fetch instruction • Goto Right instruction The ROM will depend on the CAR alone

CAR • Arithmetic = 1 micro instruction • Load = 2 micro instructions • Store = 2 micro instructions

CAR – Order of execution Assume we are executing the instruction Load …

CAR – Order of execution Assume we are executing the instruction Load …

CAR – Order of execution Assume we are executing the instruction Load …

Implementation of the Goto in the CAR circuit 1 Adder CAR C1C2 MUX 000 Instruction CAR table The Instruction

[BITS 0-4] Mirco-instructions CAR Program ROM IR PC 3 All the control in the system [BITS 13-28] [BITS 5-8] 16Registers [BITS 9-12] 0 1 1 [BITS 5-8] 5 1 0 1 2 [BITS 13-16] 0 4 [BITS 9-24] 2 [BITS 5-8] RAM 1 1 ALU 0 [BITS 9-24]

The micro-instruction ROM The micro instruction ROM depends on the CAR only now.