Dynamic Reconfigurability in Embedded Systems: Polaris Allocation and Relocation Management

80 likes | 197 Vues

The Polaris project focuses on the development of a self-dynamically reconfigurable architecture in embedded systems. It aims to automate the allocation and relocation of tasks based on specified parameters, enhancing adaptability and efficiency. Key goals include producing ready-to-use architectures with support for 1D and 2D reconfiguration, minimizing overhead, and optimizing routing efficiency. The project encompasses a comprehensive workflow for managing task allocation and includes validation tools and simulation frameworks to evaluate various placement strategies.

Dynamic Reconfigurability in Embedded Systems: Polaris Allocation and Relocation Management

E N D

Presentation Transcript

Polaris Task shapes definitions, allocation and relocation management for a self dynamically reconfigurable architecture Dynamic Reconfigurability in Embedded Systems Design

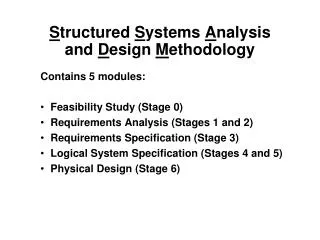

Outline • Motivations • Goals • Project Description • Subprojects: • Task allocation management • BiRF • General information

Motivations • Need for an automated way to obtain an autonomous dynamically reconfigurable system • Starting from a specification: • Target application • Target device info • Reconfiguration model (1D or 2D) • Communication Infrastructure • Produce a “ready-to-use” architecture: • Setup configuration bitstream • Partial bitstreams • Blank bitstreams • Processor executable code to manage the runtime solutin

Goals • Creation of a workflow to generate a self dynamically reconfigurable architecture with: • Support for 1D and 2D reconfiguration • Definition of “good” area constraints • Runtime task placement decisions • Internal and fast Task relocation • Performing critical architectural choices • Based on feedback from scenario simulation

Project Description • Workflow to manage allocation and relocation of tasks in self dynamically reconfigurable architectures • Final goal: complete architecture (bitstreams and code) generation

Tasks Allocation Management • Definition of Area Constraints and an Allocation manager • Desired features: • Low TRR, fragmentation, management overhead • High routing efficiency • Different “shaping” policies • Various fitting strategies: • General (First Fit, Best Fit, Worst Fit…) • Focused (Fragmentation Aware, Routing Aware… )

BiRF • Architectural support of the flow: • Validation tool for the chosen • Reconfiguration model • Communication infrastructure • Simulation framework • Monitor the reconfigurable system evolution • Evaluate different placement policies and area constraints definitions • Relocation solution suitable for the target system • BiRF, BiRF2, …

General Information • Webpage • www.dresd.org/?q=polaris • Mailing List • polaris-ml@dresd.org • Contact • To have more information regarding Polaris: • polaris@dresd.org • For a complete list of information on how to contact us: • www.dresd.org/?q=contact_polaris • Related work – wiki: • www.dresd.org/?q=soa_polaris