MONITOR ROM MODULE (MON)

MONITOR ROM MODULE (MON). Module Objective. Understand how to use the Monitor ROM, which alllows complete testing of the MCU through a single-wire interface with a host computer. IRQ. LVI. Direct Memory Access Module (DMA). System Integration Module (SIM). Clock Generation Module

MONITOR ROM MODULE (MON)

E N D

Presentation Transcript

Module Objective • Understand how to use the Monitor ROM, which alllows complete testing of the MCU through a single-wire interface with a host computer.

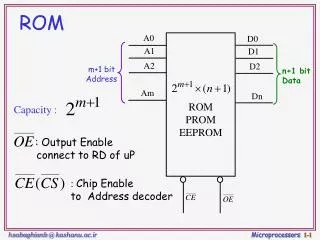

IRQ LVI Direct Memory Access Module (DMA) System Integration Module (SIM) Clock Generation Module (CGM) Timer Interface Module (TIM) 68HC08 CPU RESET COP BREAK Internal Bus (IBUS) Random Access Memory (RAM) Serial Peripheral Interface (SPI) Electronically Programmable Memory (EPROM) Monitor ROM Serial Communications Interface (SCI) MONITOR MODULE • Normal User-Mode Pin Functionality • One Pin Dedicated to Serial Communication between Monitor ROM and Host Computer • Standard Mark/Space Non-Return-to-Zero (NRZ) Communication with Host Computer • 4800 Baud–28.8 kBaud Communication with Host Computer • Execution of Code in RAM or ROM • (E)EPROM/OTPROM Programming

Monitor Mode (MON) Operation • Receives and executes commands from a host computer • Communicates via a standard RS-232 interface • Communication is standard non-return-to-zero (NRZ) • All communication between Host and MCU is through the PTA0 pin • A level-shifting and multiplexing interface is required between PTA0 and Host . • PTA0 used in a wired- OR configuration and requires a pulll-up resistor • To indicate MCU is ready to receive command • MCU sends break signal(10 consecutive logic zeros) to host computer • Break signal also provides timing reference for host to determine necessary baud rate(must be identical). • baud rate range: 4800 baud to 28.8 Kbaud • Monitor ROM immediately echoes each received byte back to the PTA0 pin for error checking

Bus Frequency PTC0 PIN PTC1 PIN PTA0 PIN PTC3 PIN Mode IRQ1/Vpp PIN CGMOUT CGMXCLK/2 or CGMVCLK/2 Monitor VDD + VHI 0 1 1 1 CGMOUT/2 1 0 VDD + VHI 1 0 Monitor CGMOUT/2 CGMXCLK Monitor ModeSelection • Three external pins examined at rising edge of RST • Conditions for entering Monitor operating mode • Enter Monitor mode by either • Executing a software interrupt instruction(SWI) or • Applying a logic zero and then a logic one to the RST pin • Reset vector fetched from $FEFE - $FEFF rather than $FFFE - $FFFF • Executes program in monitor ROM, $FE10 - $FEFF

BREAK VECTORHIGH BREAKVECTORLOW RESET VECTOR HIGH RESET VECTORLOW SWI VECTOR HIGH SWI VECTOR LOW Mode Differences FUNCTIONS MODES COP $FFFE $FFFD $FFFD USER ENABLED $FFFF $FFFC $FFFC DISABLED $FEFD $FEFC $FEFD $FEFE $FEFF $FEFC MONITOR

Command Description READ Read memory WRITE Write memory IREAD Indexed Read IWRITE Indexed Write READSP Read Stack Pointer RUN Run User Program Monitor ROM Commands

Read Byte from Memory Description Specifies 2-bute address in high byte:low byte order Operand Data Returned Returns contents of specified address $4A Opcode Command Sequence Write Byte from Memory Description Specifies 2-bute address in high byte:low byte order; low byte followed by data byte Operand Data Returned None $49 Opcode Command Sequence READ(Read memory) Command WRITE(Write memory) Command

Read next 2 bytes in memory from last address access Description Specifies 2-bute address in high byte:low byte order Operand Data Returned Returns contents of next two address $1A Opcode Command Sequence Write to last address accessed + 1 Description Specifies single data byte Operand Data Returned None $19 Opcode Command Sequence IREAD(Indexed Read) Command IWRITE(Indexed Write) Command

Reads Stack Pointer Description None Operand Data Returned Returns stack pointer in high byte:low byte order $OC Opcode Command Sequence Executes RTI intstruction Description None Operand Data Returned None $28 Opcode Command Sequence READSP(Read Stack Pointer) Command RUN(Run User Program) Command