FPD_LM

E N D

Presentation Transcript

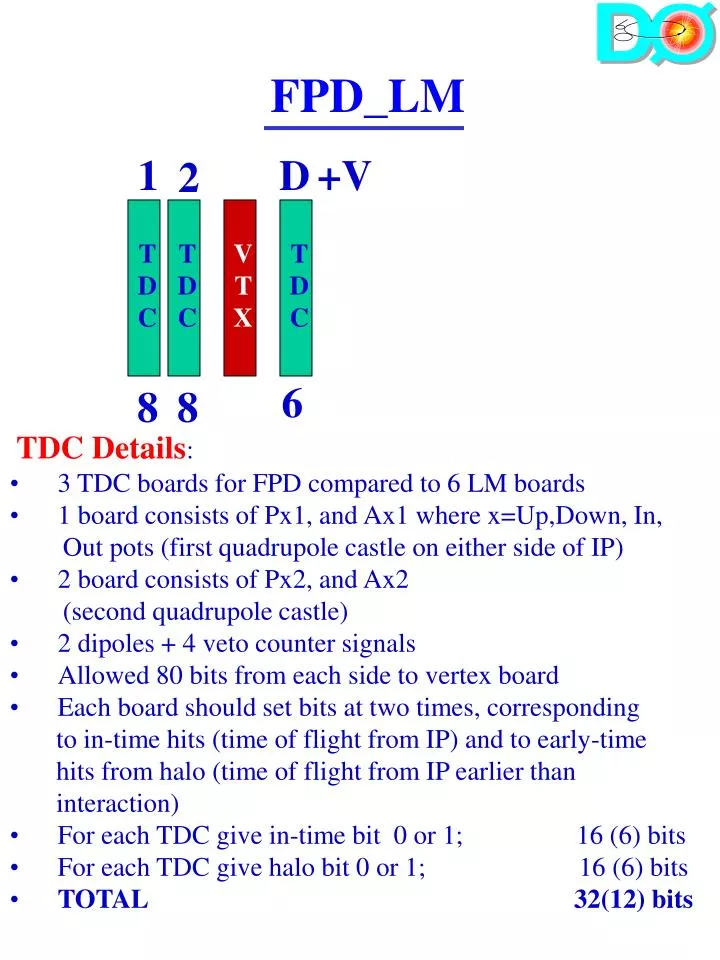

FPD_LM 1 D +V 2 T D C T D C V T X T D C 6 8 8 • TDC Details: • 3 TDC boards for FPD compared to 6 LM boards • 1 board consists of Px1, and Ax1 where x=Up,Down, In, • Out pots (first quadrupole castle on either side of IP) • 2 board consists of Px2, and Ax2 • (second quadrupole castle) • 2 dipoles + 4 veto counter signals • Allowed 80 bits from each side to vertex board • Each board should set bits at two times, corresponding • to in-time hits (time of flight from IP) and to early-time • hits from halo (time of flight from IP earlier than • interaction) • For each TDC give in-time bit 0 or 1; 16 (6) bits • For each TDC give halo bit 0 or 1; 16 (6) bits • TOTAL 32(12) bits

More TDC Details • 1 board should send 8 in-time and 8 halo bits to 2 board • which should receive these bits and send 16 in-time bits and 16 • halo bits to vertex board • D+V board should send 6 in-time and 6 early-time hits to • Vertex board • Note: cable lengths should be such that all 1 signals arrive • at 1 board at a fixed time, and all 2 signals arrive at 2 board • at a different fixed time, and D+V signals arrive at a 3rd • fixed time. Carlos should verify these times. • Steps to operational FPD TDC boards • Brendan finishes TDC firmware • Carlos ensures that signals arrive correctly at TDC boards • along with Victor determines delays for in-time and halo • for each TDC board • Victor finishes database that can download parameters • to TDC board—do any of these differ from LM paramaters • other than nclock delay and delta delay? How do • we determine other parameters (Brendan?) • Need to have VXWORKS project to modify power PC • controls—what exactly has to be done (Brendan, Victor) • Carlos should start giving documentation to PhD student • and hopefully 2nd Manchester engineer. • 5) Dave’s work (see later slide)

Vertex Details Vertex board should receive 22 in-time bits and 22 halo bits from TDC boards. It should form 4 bit words for each of the 9 spectrometers 0=no coincidence of 1+2 pots for that spectrometer 1=coincidence of 1+2 pots for that spectrometer 2=coincidence but either one of diagonally opposite spectrometer pots has halo bit set 3=coincidence but both of diag opposite pots has halo bit set Example: PU1.PU2 no early time hits in AD1 or AD2 =1 PI1.PI2 with early time hits in AO1 and AO2 =3 Vertex board passes information to TM Can pass up to 96 bits to TM in 16 bit bursts (separated by 18 nsec), 80 bits are currently needed 1 Spec 1-4 4bit words 2 Spec 5-8 4 bit words 3 Spec 9 4 bit word, 2 in-time bits from spec. 9, 2 halo bits from spec. 9, 4 veto counter in-time, 4 VC halo bits 4 16 in-time bits from spec 1-8 5 16 halo bits from spec 1-8

Dave’s work • Get Verilog code to compile, understand TDC board • thoroughly • Add scalar information from each channel, both in-time • and early, get this information into EPICS • Pass information from TDC boards to Vertex boards • Program Vertex boards

Trigger Manager Inputs 1x96 FPD_LM T M 1x96 LM 3x96 FPD_DFE • FPD_LM 80 bits of information on 9 spectrometers • and veto counters—see previous slide, • 2) LM TL 8 bits (50 psec resolution) • TR 8 bits • Fast Z 6 Bits • #N counters 5 bits • #S counters 5 bits • 16 LM and/or terms • 3) DFE 12 bits/track for up to 7 tracks (need format • from Ricardo)

Real Steps to Triggering • Don’t trigger, just readout all events • And/or terms from SCR:Diff_x (x=PU,… 5 in all) • Diff_any, Elas_x (2), Elas (1), DPOM ( • up_up, dn_dn, dipole_up, dipole_dn,any): • bypass TM • Add DFE to TM (with no LM or FPD_LM). First use multiplicity cut to reject halo sprays. Estimated rejection? Expect at least 10. • Add trigger equations, this will rule out invalid • combinations, allow selection of high-t. Reduce MI • background. Estimated rejection? • 5) Add L2 Gap tool, L3 tools • 6) If LM TDC boards are ready, but no vertex board, • can we send signals to TM? Replace functionality • of vertex board in TM? • 7) Once vertex board works, can apply single interaction algorithm. • 8) Add in FPD_LM information and disable SCR and/or terms

Trigger Manager Logic • Set and/or terms • For each track, check that spectrometer word =1 • (in-time coincidence, no halo) • 2) Compare ,t with trigger list and set and/or terms

FPD Triggers • The FPD Trigger Manager allows cuts on =1-p/p and t, and • also incorporates information from the trigger scintillator via • the LM boards. • A track is defined as two detector hits in any spectrometer with • a valid x and t, a trigger scint. confirm, and no halo veto set. • AND-OR term definitions: • RTK = track in any spectrometer, (D= veto on halo) • RPT = proton track RAT = anti-proton track • RTK(1) x > 0.99, all t • RTK(2) 0.99 > x > 0.9 all t • RTK(3) x > 0.9 all t, no halo veto • RTK(4) x > 0.9, |t|>1 GeV2 • RTK(5) x > 0.9, all t • REL = Elastic (diagonally opposite p and ) • ROV = Overconstrained track (D+Q proton tracks) • REL(1) = x > 0.99, all t • REL(2) = x > 0.99, |t | > 1 GeV2 • ROV(1) = x > 0.90, all t • ROV(2) = x > 0.90, |t | > 1 GeV2) • LMO = no hits in LM; LMI(1) = Single Interaction; • LMD=N+Sbar .OR. S+Nbar 16 AND-OR terms allocated to implement all FPD triggers (13 currently in use)