Registers and Counters

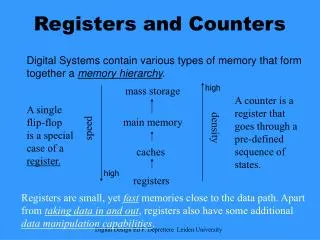

Registers and Counters. D. Q. Q. C. Last Lecture. Last time we looked at: latches flip flops We saw that these devices hold a value depending on their inputs. A data input value is loaded into the register on the rise of the clock edge.

Registers and Counters

E N D

Presentation Transcript

D Q Q C Last Lecture • Last time we looked at: • latches • flip flops • We saw that these devices hold a value depending on their inputs. • A data input value is loaded into the register on the rise of the clock edge. • Some circuits have additional ~clear or ~reset inputs. Positive edge- triggered flip-flop

Registers from Latches • Often want to read a group of data inputs into a set of latches at the same time (e.g. reading a 4 bit value off a computer bus) • A group of latches can be combined to form a register • A 4 bit register can be made from 4 latches

D0 D Q Q0 C clk D0 Q0 D1 D Q Q1 Q1 D1 C D2 Q2 D Q Q2 D2 C D3 Q3 clk D3 D Q Q3 C Four bit Register Symbol Circuit

Qa Qb Qc Qd Da D Q D Q D Q D Q C C C C A B C D Qa Qb Qc Qd 0 0 1 0 1 0 0 1 1 1 0 0 0 1 1 0 0 0 1 1 0 0 0 1 • Da =1: Initial Values • after clock 1 • after clock 2 • Da = 0: after clock 3 • after clock 4 • after clock 5 Shift Registers • Allow stored data to be moved from one bit position to another

Shift Registers • Points to note: • At every clock pulse, the first flip flop is loaded with the value of the data in stream • The data that was in this flip flop is then loaded into the second and so on. • The data can be taken out of the last flip flop in serial form or it can be taken from all outputs at the same time – parallel form.

Qa Qb Qc Qd Da D Q D Q D Q D Q C C C C A B C D Shift Registers • For each flip flop there is a delay between clock pulse and output. This delay provides time for the next flip flop in the chain to load the data from the previous stage. data clock Qa Qb etc

Shift Registers • Shift registers can also be loaded using parallel input lines • Therefore inputs can be parallel or serial • Outputs can be parallel or serial • Functions that shift registers can carry out include: • Serial Loading • Serial Output • Parallel Output • Parallel Loading • This makes them suitable for a wide variety of tasks

Shift Registers • A large variety of integrated circuit (IC) shift registers are available with various combinations of • serial and/or parallel input • serial and/or parallel output • shift left and/or shift right • Applications include: • Converting a parallel word into serial form or vise versa • performing a number of logical and arithmetic operations (binary multiplication/division involves shifting).

D C invalid Q tpd thold tset-up Registers • Timing characteristics for edge-triggered registers • propagation delay (tpd) defined as the time between the clock edge and the output changing • Set-up (tsetup) and hold (thold) times are the times which the data must be held steady before and after the clock edge

Counters • Counters may be clocked by: • regular clock pulses to determine a certain time duration • random pulses to count the occurrences of a particular event • Most common counters count natural binary sequence up down counter counter 000 111 001 110 010 101 011 100 100 011 101 010 110 001 111 000 000 111 ... ...

JK Flip flop - recall • A JK flip flop toggles when both inputs are 1. In this case it effectively counts every second clock pulse: J Q 1 clock ~Q K You can also say it counts from 0 to 1 and back again. clock Q Sometimes called a “scale of 2 counter”

Counters Q1 Q2 1 • Connect two such flip flops together: 1 clock Complete the timing diagram for Q2 clock Q1 Q2 Outputs Q1 and Q2 cycle. Q2Q1: 00 01 10 11 00

Q Q J J K Q K Q Counters • Ripple (asynchronous) Counter • e.g. A 3 bit ripple counter using negative edge triggered JK flip-flops • Asynchronous means each flip flop is triggered by the preceding one. Qa Qb Qc 1 1 1 Q J clk 1 1 1 K Q

0 1 1 0 1 0 0 0 0 1 0 0 Counters 1 0 0 2 0 0 • These propagation delays cause a number of sequence changes when going from one number to the next, which can be undesirable in a lot of situations. • The counter can get the wrong value at a particular instant in time • Operating speed is therefore limited. Qc Qb Qa C

Qb Qa 1 Q J Q J 1 K Q K Q clk Counters • Synchronous counters • Outputs of all the flip-flops change at the same time • e.g. a 2-bit synchronous counter 1 C 0 1 Qa 0 1 Qb 0 00 01 10 11 00 01

Q J K Q Counters • Synchronous counters • Does this extend to a three bit counter? • Qc should not toggle until both Qa and Qb are 1 ? Qb Qa Qc 1 Q J Q J 1 K Q K Q clk

Qb Qa Qc 1 Q J Q Q J J 1 K Q K Q K Q clk Counters • Synchronous counters • e.g. A three bit counter • e.g. A four bit counter Qb Qa Qc Qd 1 Q J Q Q Q J J J 1 K Q K Q K Q K Q clk

Counters Ripple Carry Output • An integrated circuit counter • Many forms of counters available as integrated circuits • e.g. 74163 - four bit synchronous binary up counter • Clock: count advanced by 1 on • Clear: when = 0 count reset to 0 on next clk • Load: when = 0 count set to values on A-D on next clk • Enable T & P: Counting disabled when either is equal 0 • Qa, Qb,Qc,Qd: state of the counter • Ripple Carry output : = 1 when count = 1111 otherwise 0 T Enable Load Vcc Qa Qb Qc Qd 16 15 14 13 12 11 10 9 Ripple Carry Output Qa Qb Qc Qd T Enable Load Clear Enable P clk A B C D 1 2 3 4 5 6 7 8 Clear clk A B C D Enable P GND

163-3 163-2 163-1 clk clk clk carry carry carry T T T P P P Qd Qc Qb Qa Qd Qc Qb Qa Qd Qc Qb Qa Counters • An integrated circuit counter • In many cases more than 16 states required for counting • counters like 163 can be cascaded to form larger counters

Counters • Modulo-n counters • A modulo-n counter generates n states before it repeats itself • e.g. a 2 bit count is modulo 4 and a 4 bit counter is modulo 16 • Often a counter which has a modulo that is not a power of 2 is required e.g. modulo 12 1 load 0 1 0 0 clk clear load D C B A Qd Qc Qb Qa clk carry 1 clear Qd Qc Qb Qa Counts from 0 through to 11 before being reset Counts from 4 through to 15 before being set to 4 again

1 C 0 1 Qa 0 1 Qb 0 Counters • Frequency division • Binary counters offer the possibility of frequency division • Often used where clocks of different frequencies are required in a circuit or to produce a compact accurate low frequency oscillator (e.g. an oscillator for a digital watch) f 1/2f 1/4f

Registers/Shift registers and Counters • Summary • Registers consist of a group of D-type latches or flip-flops which are clocked simultaneously to store a binary word • set-up and hold times must be observed • Shift registers allow data to be moved from one bit position to another • used for parallel«serial conversion and some types of arthmetic operations • Counting is a common requirement in sequential logic circuits • Counters can be asynchronous or synchronous • Many IC packages exist which implement counters

What you should be able to do • Explain the operation of a register • Explain the propagation delays associated with registers • Outline the use of registers for converting serial/parallel inputs/outputs. • Explain the operation of ripple (asynchronous counters) • Explain the operation of synchronous counters • Outline the characteristics of modulo n counters.