Milton Godwin Applied Materials, US

350 likes | 515 Vues

ITRS 2000 Conference Dec. 6th, 2000 Hsinchu, Taiwan, R.O.C. Defect Reduction Cross-Cut Technology Working Group 2000 Updates. Toshihiko Osada Fujitsu, Japan. Milton Godwin Applied Materials, US. Chris Long IBM , US. Outline. Yield Cycle 2001 ITRS DR ITWG Co-chairs

Milton Godwin Applied Materials, US

E N D

Presentation Transcript

ITRS 2000 Conference Dec. 6th, 2000 Hsinchu, Taiwan, R.O.C.Defect Reduction Cross-Cut Technology Working Group2000 Updates Toshihiko Osada Fujitsu, Japan Milton Godwin Applied Materials, US Chris Long IBM , US

Outline • Yield Cycle • 2001 ITRS DR ITWG Co-chairs • 2000 “Soft” Table Updates • 2001 Challenges

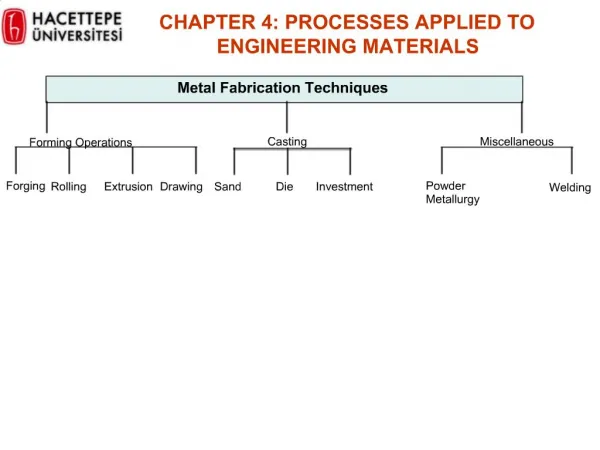

Defect Reduction TWG Yield Learning Cycle Focus Topics Yield Model and Defect Budget Defect Detection Defect Sources and Mechanisms Defect Prevention and Elimination Process to Process Interactions Design to Process Interactions Process Materials Process Equipment Wafer/Pkg Environment Parameter Control Validation/Enhancement of Yield Models

United States Milt Godwin Applied Materials MDR Christopher Long IBM Taiwan Len Mei ProMOS Tech, Inc. Korea D.H. Cho Samsung H.J. Kwon Hyundai Europe Venkat Nagaswami Philips Lothar Pfitzner Fraunhofer Institute Japan Toshihiko Osada Fujitsu Fumio Mizuno Hitachi 2001 ITRS DR ITWG Co-chairs

Yield Model Defect Budget Tables 76-77 Key 2000 Updates • Table 76: Yield Model and Defect Budget MPU • Technology Requirements • Table updated to reflect changes made to the Overall Roadmap Technology Characteristics (ORTC) Tables with respect to year/technology node, chip size and device pitch. • Additionally an error in Random D0 calculation was caught and fixed. • Table 77: Yield Model and Defect Budget DRAM • Technology Requirements • Table was updated to reflect changes made to the Overall Roadmap Technology Characteristics (ORTC) Tables with respect to year/technology node, chip size and device pitch.

Table 76: Yield Model Defect BudgetMPU Technology Requirements: Was vs. Is

Table 76: Yield Model Defect BudgetMPU Technology Requirements: Was

Table 76: Yield Model Defect BudgetMPU Technology Requirements: Is

Table 76: Yield Model Defect BudgetDRAM Technology Requirements: Was vs. Is

Table 76: Yield Model Defect BudgetDRAM Technology Requirements: Was

Table 77: Yield Model Defect BudgetDRAM Technology Requirements: Is

Defect Detection Table 78 Key 2000 Updates • ITRS Node definition updated to reflect changes made to the ORTC Tables with respect to year/technology node. Used for reference and perspective. • R&D, Process, and Manufacturing Scan Speeds adjusted to a practical user standpoint as follows: -R&D scan speed remained the same, but an additional reference to # wafers scanned per hour included. • -Process scan speed adjusted to a 4 wafer per hour level, which relates to expectations from mfg. -Manufacturing scan speed adjusted to a level of desire for capturing defects of the size noted in the chart.

Defect Detection Table 78 Key 2000 Updates • In order to comply with ORTC guidelines, Critical defect size was doubled • -R+D 0.3X GR -> 0.6XGR • -Yield Ramp 0.5X GR -> 0.8XGR • -Volume Production 0.5X GR -> 1.0XGR • High Aspect Ratio defect sizes adjusted to equal Volume Manufacturing sizes at 1 X design rules. This is desired level dependent on the specific ratio.

Defect Detection Table 78 Key 2000 Updates(cont.) • Backside particle size line was deleted due to no capability to measure defects at the size noted on 200mm wafers. Very little data exists for 300mm and no defect size projections have been made. • Defect Review: Now labeled for Patterned Wafer. Un-Patterned review is just now being documented and is scan tool sensitive. • Defect Review: Coordinate Accuracy at the Defect Sizes noted in the “Volume Manufacturing” Size numbers give a more understandable and direct measure for manufacturing personnel to relate to.

Table 78A: Defect DetectionTechnology Requirements: Was vs. Is – Short Term Years

Table 78B: Defect DetectionTechnology Requirements: Was vs. Is – Long Term Years

Defect Sources and Mechanisms: Table 79 Key 2000 Updates • ITRS Node definition updated to reflect changes made to the ORTC Tables with respect to year/technology node. Used for reference and perspective.

Table 79A: Defect Sources and Mechanisms Technology Requirements: Was vs. Is – Short Term Years

Table 79B: Defect Sources and Mechanisms Technology Requirements: Was vs. Is – Long Term Years

Defect Prevention and Elimination: Table 80 Key 2000 Updates • ITRS Node definition updated to reflect changes made to the ORTC Tables with respect to year/technology node. Used for reference and perspective.

Table 80A: Defect Prevention and EliminationTechnology Requirements: Was vs. Is – Short Term Years

Table 80A: Defect Prevention and EliminationTech. Requirements: Was vs. Is – Short Term Years (cont.)

Table 80A: Defect Prevention and EliminationTech. Requirements: Was vs. Is – Short Term Years (cont.)

Table 80A: Defect Prevention and EliminationTechnology Requirements: Was vs. Is – Long Term Years

Table 80A: Defect Prevention and EliminationTech. Requirements: Was vs. Is – Long Term Years (cont.)

Table 80A: Defect Prevention and EliminationTech. Requirements: Was vs. Is – Long Term Years (cont.)

Yield Model and Defect Budget Key Issues for 2001 • Redundancy model for MPU, DRAM, SoC • Benchmark fixability rates • Develop calculator to use to determine what numbers mean “to you” • Series of algorithms that show how to use the tables • Update defect budget projections based on inputs from Japan and US companies • Quantify placement of yellow and red in tables based on learning rates • Re-validate systematic limited yield assumptions • Address New processes/New Materials • Need to include Cu & Low Dual Damascene BEOL • High K Gate Dielectric

Defect Detection Key Issues for 2001 • Inspection of contacts and vias major issue, find defects in 10:1 AR structures • HARI, Need Definition on: • Throughput, Defect Nature, Aspect Ratio, Feature size/shape type; Red at 120, at least • Ability to inspect at .5X GR • Change in inspection speed requirement • R&D Section • Red at 54, 0.3wfr/hr (previously inaccurate) • Yield Ramp • Move to 2 wfrs/hr, Yellow at 96, Red at 56 • Volume • Keep 10 wfr/hr, Yellow at 150 • Major Issue – Redefine as CoO to include space/ capital ~ $5 target, ~ $3 Goal

Defect Sources and Mechanisms Key Issues for 2001 • Need to redefine defect sourcing complexity factor • Develop an algorithm for “time to recognize trends” • Add a “Defect Remediation” section • Add production considerations to table. • Fault- vs. defect-centric approach • Data acquisition • storage/archival/retrieval/analysis/correlation capabilities + time • Merging DMS databases with tool databases

Defect Prevention and Elimination Key Issues for 2001 • Continue to emphasize PoO guideline – not specs • Reassess categories and contaminants, e.g. “new” material categories critical vs. non-critical • Address issue of variability (vs. absolute requirement) • Need to capture (summarize) metrology concerns related to Table 80 • Wafer Environmental Control • What is justification for decreasing AMC levels – Need discussion • UPW, Chemicals,Gases, New materials • Specifics need to be addressed • Trace metals and inorganics producing effects in gates that are reliability issues.

Other Issues for DR in 2001 ITRS UpdateApproaching 100nm • Margin-less process (for features) • photo, etch, CMP need • Single wafer equipment • Need integrated monitoring (current monitors off-line) • Monitor hardware needs to be robust in operating environment • SoC • SRAMs • are small and nuerous in design • Represent large total of non-redundant structures • Change in design methodology • Design for Test • DFT to overcome testing issue-generally only two pins available • Yield loss due to AMHS • No monitor for mis-handling • Need automated monitor/feedback that does not add appreciable cycletime • Need to drive improved process tool matching

Other Issues for DR in 2001 ITRS UpdateSub- 100nm • New Device Structures should be robust for process margin and defects • Gate Ox to include RTP • How to check process margins • Not currently modeled • Intelligent equipment needed to recover process window • New material and impact on yield • Cooperation between vendors and manufacturers required • New method needed for defect detection (e-beam)

US DR Domestic TWG MeetingOct 2000 (Complete) • Discussed Proposed Name Change • Defect Reduction -> Yield Management • YMDB -remains the same • DD -> DD and Characterization • DSM - > Integrated Yield Management Technology • DPE -> Environmental and Consumable Contamination Control