Relational Operators

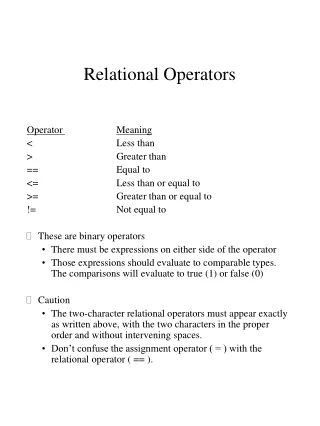

Relational Operators. Result is boolean: greater than (>) less than (<) inequality (/=) greater than or equal to (>=) less than or equal to (<=) equal (=). Relational Operators. Operands must be of same type Arrays maybe of different lengths Aligned left and compared.

Relational Operators

E N D

Presentation Transcript

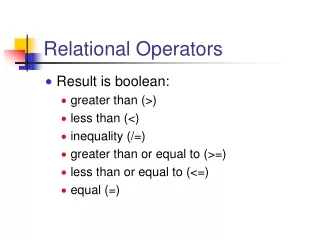

Relational Operators • Result is boolean: • greater than (>) • less than (<) • inequality (/=) • greater than or equal to (>=) • less than or equal to (<=) • equal (=)

Relational Operators • Operands must be of same type • Arrays • maybe of different lengths • Aligned left and compared

VHDL Modelling Concepts • Constants (value remains the same) • Variables (similar to variables in a programming language) • Signals (has to be able to model timing behaviour)

Signals • For example consider a NAND gate: • C will be scheduled to change 3ns after A or B changes • A signal has an event when the signal value is changed NAND1 :process (A, B) begin C <= A NAND B after 3ns; end process NAND1; A C B

A C Signals B NAND1 :process (A, B) begin C <= A NAND B after 3ns; end process NAND1; test : process begin A <= '0'; B <= '0'; wait for 10 ns; A <= '1'; wait for 10 ns; B <= '1'; wait; end process test;

test : process begin gate <= '0'; A <= '1'; B <= '1'; wait for 10 ns; gate <= '1'; wait; end process test; A C Concurrency gate F B • VHDL is designed to model the concept of concurrency • E.g. Consider 2 NAND gates defined in separate processes

Process States • Each process can be in one of three states: Suspended Execution Complete Signal Event Running Active

3 ns At T = 13 : T is updated NAND : T <= 0 at T = 13 NAND NOR NAND A T NAND Example 3 B NOR C At T = 10 : A <= ‘1’; NAND NOR Suspended Execution Complete Signal Event Running Active

The Simulation Cycle • One point in simulation time • Simulation cycle consists of: • Updating Signal Values • activate dependant processes • Execute each active process until it suspends • generate new update list • may cause more processes to be triggered in current cycle!

Example 4 architecture gate of l5_e2 is signal a, M : bit; begin p1: process (A,M) begin M <= A; Y <= M; end process p1; p2 : process (m) begin Z <= M; end process p2; end gate;

Question • Why should the following be avoided: entity quest is end quest; architecture question of quest is signal a : bit_vector (3 downto 0); begin A <= A NAND "0001"; end question;

Concurrent and Sequential Statements • VHDL can model both concurrent and sequential behaviour If, case, loop, null, wait, next, exit, signal assignment, variable assignment, procedure call, assert Block, process, generate, signal assignment, procedure call, assert, component instantiation

Sequential Statements • Statements executed in same order as high level programming language • May only appear inside a process statement, procedure or function

Variable Assignment • variable is updated at time the assignment takes place • target and expression types must be the same • NOTE local variables only visible inside process Variable_assignment_statement ::= target := expression

Example 5 architecture question of var_eg is begin p1: process variable a, b, c, d : std_logic_vector ( 3 downto 0); begin a := (others => '0'); c := "0001"; d := ( 2 downto 1 => '0', others => '1'); a := c and d; b := a or d; wait; end process p1; end question;

Signal Assignment • Value is updated when process is suspended • Note different delimiter <= verses := signal_assignment_statement ::= target <= waveform_element {,waveform_element} wave_form_element ::= value_exp [after time_exp]

Example 6 architecture question of var_eg is signal a, b : std_logic_vector ( 3 downto 0); begin p1: process variable c, d : std_logic_vector( 3 downto 0); begin a <= (others => '0'); c := "0001"; d := ( 2 downto 1 => '0', others => '1'); a <= c and d; b <= a or d; wait for 10 ns; b <= a or d; end process p1; end question;

If Statement • Similar to those found in high level programming languages if_statement ::= if condtion then sequential_statements {elsif condtion then sequential_statements} [else sequential_statements] end if;

Example 7 p1: process (x, b) begin if (x = '1') then a <= b; end if; end process p1;

Example 8 p1: process (x, b) begin if (x = '1' and x'event) then a <= b; end if; end process p1;