Ultra-Low Power Wireless Micro-Sensor Node for Acoustic Applications

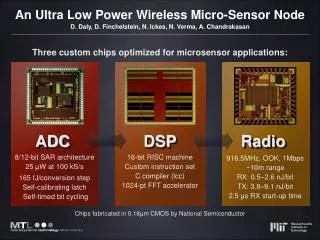

This paper presents three custom chips optimized for micro-sensor applications, demonstrating ultra-low power performance. The design includes an 8/12-bit SAR architecture, achieving 25 µW at 100 kS/s, with a remarkable 165 fJ per conversion step. Key features of the micro-sensor node include a self-calibrating latch, self-timed bit cycling, and a 16-bit RISC machine. The chips enable efficient acoustic target classification using FFT acceleration, with low transmission power of 3.8–9.1 nJ/bit, making it ideal for battery-operated applications requiring a compact footprint.

Ultra-Low Power Wireless Micro-Sensor Node for Acoustic Applications

E N D

Presentation Transcript

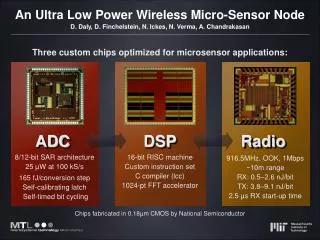

An Ultra Low Power Wireless Micro-Sensor Node D. Daly, D. Finchelstein, N. Ickes, N. Verma, A. Chandrakasan Three custom chips optimized for microsensor applications: ADC DSP Radio 8/12-bit SAR architecture 25 µW at 100 kS/s 165 fJ/conversion step Self-calibrating latch Self-timed bit cycling 16-bit RISC machine Custom instruction set C compiler (lcc) 1024-pt FFT accelerator 916.5MHz, OOK, 1Mbps ~10m range RX: 0.5–2.6 nJ/bit TX: 3.8–9.1 nJ/bit 2.5 µs RX start-up time Chips fabricated in 0.18µm CMOS by National Semiconductor

FPGA for radio clock/data recovery All other functions performed by chipset Credit-card sized node Discrete power regulators, acoustic front end System Integration A complete acoustic sensor node Lithium battery Power Management/Regulation Preamp ADC I/F FFT accelerator Radio I/F RX BB RF ADC ADC SRAM FPGA PA CPU Microphone Power Regulators Radio RX Antenna ADC TX Antenna DSP FPGA Microphone

Example Application Benchmark Acoustic target classification Sample microphone Compute FFT Identify peaks Send to base station > < 1500 3.8 mW peak ~ 1000 Power (µW) Radio ADC 500 DSP 0 0 50 100 150 200 250 Time (ms)