ARM Instruction Set Overview: Arithmetic, Logic, and Memory Operations

This document provides a comprehensive overview of the ARM instruction set, focusing on arithmetic, logical, comparison, test, and memory transfer operations. Each instruction is detailed with its mnemonic, operation code, and the condition flags it affects, such as Negative (N), Zero (Z), Overflow (V), and Carry (C). The guide outlines various instructions including addition, subtraction, multiplication, logical operations, and data transfer methods, along with their corresponding formats and modes. This serves as a valuable reference for developers and engineers working with ARM architecture.

ARM Instruction Set Overview: Arithmetic, Logic, and Memory Operations

E N D

Presentation Transcript

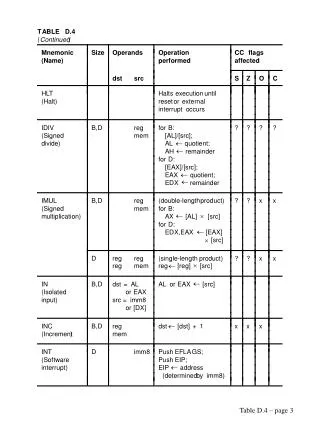

. . . T ABLE B.2 ARM arithmetic instructions Mnemonic OP co de Operation CC flags (Name) performed affected if S = 1 b b N Z V C 24 21 ADD 0 1 0 0 R d [R n ] Op er2 x x x x + (Add) ADC 0 1 0 1 R d [R n ] Op er2 [C] x x x x + + (Add with carry) – SUB 0 0 1 0 R d [R n ] Op er2 x x x x (Subtract) – – SBC 0 1 1 0 R d [R n ] Op er2 [C] 1 x x x x + (Subtract with carry) – RSB 0 0 1 1 R d Op er2 [R n ] x x x x (Reverse subtract) – – RSC 0 1 1 1 R d Op er2 [R n ] [C] 1 x x x x + (Reverse subtract with carry) MUL (See R d [R m ] [R s ] x x (Multiply) Figure B.4) MLA (See [R m ] [R s ] [R n ] x x R d + (Multiply Figure B.4) accum ulate)

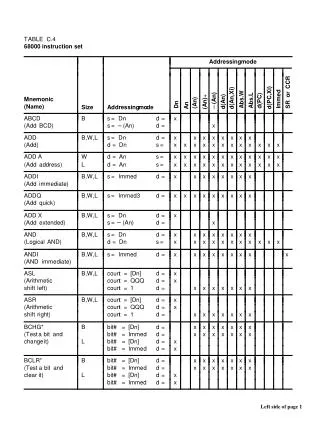

. . . T ABLE B.3 ARM logic, compare, test, and move instructions Mnemonic OP co de Operation CC flags (Name) performed affected if S = 1 b b N Z V C 24 21 AND 0 0 0 0 R d [R n ] Oper2 x x x ^ (Logical AND) _ ORR 1 1 0 0 R d [R n ] Oper2 x x x (Logical OR) EOR 0 0 0 1 R d [R n ] Op er2 x x x (Exclusiv e-OR) BIC 1 1 1 0 R d [R n ] Oper2 x x x ^ (Bit clear) _ CMP 1 0 1 0 [R n ] Op er2 x x x x (Compare) CMN 1 0 1 1 [R n ] Op er2 x x x x + (Compare Negative) TST 1 0 0 0 [R n ] Op er2 x x x ^ (Bit test) TEQ 1 0 0 1 [R n ] Op er2 x x x (T est equal) MO V 1 1 0 1 R d Op er2 x x x (Mo v e) MVN 1 1 1 1 R d Op er2 x x x (Mo v e Complement)

T ABLE B.5 ARM instructions for multiple word transfers from/to memory Mnemonic Instruction Operation (Name) bits performed P U L LDMIA/LDMFD 0 1 1 R , … , R [[R n ]] , [[R n ] + 4] , … low high (Increment after/ F ull descending) … , LDMIB/LDMED 1 1 1 R , R [[R n ] + 4] , [[R n ] + 8] , : : … low high (Increment before/ Empty descending) – … LDMD A/LDMF A 0 0 1 R , : , R [[R n ]] , [[R n ] 4] , : : … high low (Decrement after/ F ull ascending) – – … LDMDB/LDMEA 1 0 1 R , , R [[R n ] 4] , [[R n ] 8] , : : … high low (Decrement before/ Empty ascending) … STMIA/STMEA 0 1 0 [R n ] , [R n ] + 4 , … : [R ] , : : , [R ] low high (Increment after/ Empty ascending) STMIB/STMF A 1 1 0 [R n ] + 4 , [R n ] + 8 , : : : [R ] , : : , [R ] … … low high (Increment before/ F ull ascending) – … … STMD A/STMED 0 0 0 [R n ] , [R n ] 4 , : : [R ], , : : : , [R ] high low (Decrement after/ Empty descending) – – … … STMDB/STMFD 1 0 0 [R n ] 4 , [R n ] 8 , : : [R ] , : , [R ] high low (Decrement before/ F ull descending)

T ABLE B.6 ARM instructions for status register transfers, software interrupt, and data swap Mnemonic Instruction Operation (Name) formats performed MRS User mo de: (Copy status MRS R d ,CPSR R d [CPSR] register) Privileged mode: MRS R d ,CPSR R d [CPSR] MRS R d ,SPSR R d [SPSR mo de ] MSR User mo de: (W rite to status MSR CPSR,R m CPSR [R m ] – – 31 28 31 28 register) MSR CPSR,imm32 CPSR imm 32 – – 31 28 31 28 Privileged mode: MSR CPSR,R m CPSR [R m ] MSR CPSR flg,R m CPSR [R m ] – – 31 28 31 28 MSR CPSR flg,imm32 CPSR imm32 – – 31 28 31 28 MSR SPSR,R m SPSR mode [R m ] MSR SPSR flg,R m SPSR mode [R m ] – – 31 28 31 28 MSR SPSR flg,imm32 SPSR mode imm 32 – – 31 28 31 28 SWI SWI imm24 R14 sv c up dated[PC]; (Soft w are SPSR sv c [CPSR]; in terrupt) PC 0x08 SWP SWP R d ,R m ,[R n ] R d [[R n ]]; (Sw ap) [R n ] [R m ]