Timing-Aware Exception Handling in Precision Timed Architectures

Explore the necessity of exception handling in meeting timing requirements, focusing on clang/LLVM compiler infrastructure for implementation in open-source code base. Features code rewriting, static analysis, and SPARC V8 code generation.

Timing-Aware Exception Handling in Precision Timed Architectures

E N D

Presentation Transcript

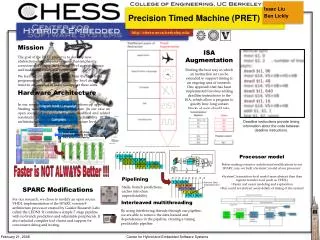

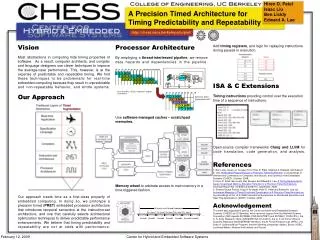

Ben Lickly Hiren D. Patel Timing-aware Exceptions for a Precision Timed (PRET) Target • Time-based Exceptions • In some cases it may be necessary to specify what happens in case a timing requirement is not met. In these cases, we would like to specify exception handling code that will handle missed deadlines. • We intend to to use the clang/LLVM compiler infrastructure as the base for our exception implementation. This is an open-source code base written with an emphasis for simplicity and extensibility. Relevant features include: • Source code rewriting • Static analysis • Code generation for SPARC V8 • References • 1. Ben Lickly, Isaac Liu, Sungjun Kim, Hiren D. Patel, Stephen A. Edwards and Edward A. Lee, Predictable Programming on a Precision Timed Architecture, in proceedings of International Conference on Compilers, Architecture, and Synthesis from Embedded Systems (CASES), October, 2008.. • 2. Hiren D. Patel, Ben Lickly, Bas Burgers and Edward A. Lee, A Timing Requirements-Aware Scratchpad Memory Allocation Scheme for a Precision Timed Architecture, Technical Report No. UCB/EECS-2008-115, September, 2008. • 3. Shanna-Shaye Forbes, Hugo A. Andrade, Hiren D. Patel and Edward A. Lee. An Automated Mapping of Timed Functional Specification to A Precision Timed Architecture, In proceedings of the 12-th IEEE International Symposium on Distributed Simulation and Real Time Applications, (DSRT), October, 2008. • Acknowledgement • This work was supported in part by the Center for Hybrid and Embedded Software Systems (CHESS) at UC Berkeley, which receives support from the National Science Foundation (NSF awards #0720882 (CSR-EHS:PRET) and #0720841 (CSR-CPS)), the U. S. Army Research Office (ARO#W911NF-07-2-0019), the U. S. Air Force Office of Scientific Research (MURI #FA9550-06-0312), the Air Force Research Lab (AFRL), the State of California Micro Program, and the following companies: Agilent, Bosch, HSBC, Lockheed-Martin, National Instruments, and Toyota. PRET Philosophy The traditional abstractions used in computer systems only concern themselves with the “functional” aspects of a program. This allows the use of techniques like speculative execution, caches, interrupts, and dynamic compilation that offer improved average-case performance at the expense of predictable execution times. The PRET project aims to improve the timing predictability at all layers of abstraction by carefully reexamining and reworking various architectural and compiler advancements with an eye toward their effects on timing behavior and worst-case bounds. . • Programming Models • One of the models of computation that seems to fit very well with the PRET architecture is Giotto. • Advantages: • Time-triggered tasks map very well onto PRET hardware threads with timing instructions • Leverage existing C code generation infrastructure of Ptolemy II to automatically synthesize PRET programs from Ptolemy’s Giotto models. clang/LLVM Compilation Even though the PRET project encompasses all the abstraction layers of a computer system, this poster primarily focuses on the middle layers, such as the instruction-set architecture, compilers and code generators, and specification languages. . Ptolemy II Code Generation ISA Extensions The instruction-set architecture is augmented with timing instructions, which control the execution time of the sequence of assembly instructions that they surround. In the code to the right, the red deadline instructions specify the timing of the enclosed code. Center for Hybrid and Embedded Software Systems