High Speed Cable Testing

High Speed Cable Testing. Twinax cable FPGA based test system BERT Eye diagrams Upgrade to system Spice simulations of eye diagrams Outlook. Twinax Cable 30 AWG CCA Sample provided by Vitaliy Fadeyev (UCSC). Uses suitable radiation tolerant plastics for insulation and jacket.

High Speed Cable Testing

E N D

Presentation Transcript

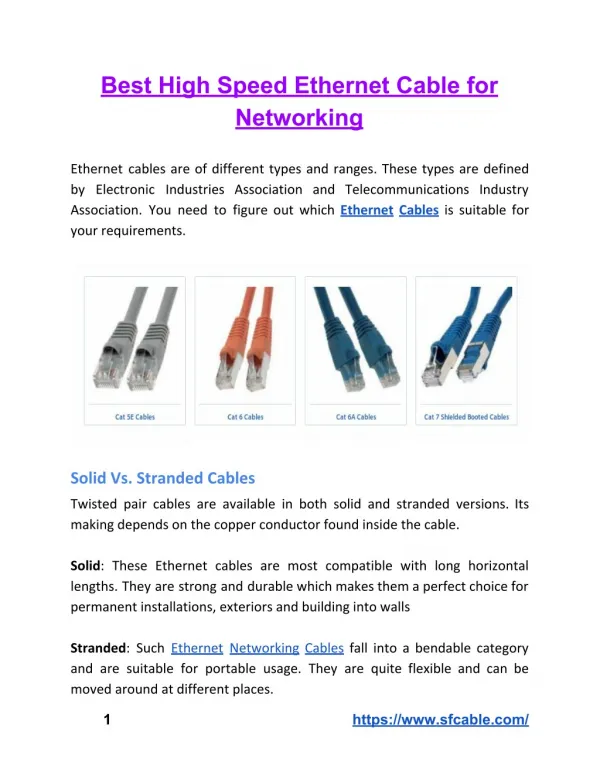

High Speed Cable Testing • Twinax cable • FPGA based test system • BERT • Eye diagrams • Upgrade to system • Spice simulations of eye diagrams • Outlook Tony Weidberg

Twinax Cable 30 AWG CCA Sample provided by Vitaliy Fadeyev (UCSC) Uses suitable radiation tolerant plastics for insulation and jacket. polyethylene and polyurethane.

FPGA Test System Sends PRBS in loopback Calculates BER Probe returned signal to get eye diagrams using high speed probe & communication analyser Probe: 7 GHz Communications analyser bandwidth>80 GHz. gtx sata port up to 7.5 Gbps

FPGA Test System • Operate at 4.5 Gbits/s (similar to VL 4.8) • Can use encoding and pre-emphasis but not done so far. • 7 bit PRBS • Can achieve low BER ~ 10-12 but this is not the full story. • For 1m worked with no pre-emphasis. • 9m 3 Gbps 1300 mv drive 17 % pre emphasis BER = 2.27 x 10-12

Eye Diagrams Source Receiver after 1m cable

Running in ‘scope mode • Send simple sequence: single “1” followed by 19 “0”s. Receiver Source Problem is caused by reflections at start of cable. Reflections in one sequence appear in next.

Solutions • Fast buffer chip at edge of PCB • Two options being considered

Solution-1 • A CML Driver board is being developed which will plug into the sata connector and enable a clean reflection free signal to be driven. • The cable will be terminated at 100 W for eye diagram tests. • Once acceptable eye diagrams have been achieved the cable will be looped back to the FPGA for BER testing and eye diagrams for the end of the cable. • Start with 1m cable and then try longer lengths. • Digital input. Reflection ignored

SY56216R • SY56216R CML Dual channel buffer to plug into SATA connector and drive test cable. • Termination should greatly reduce reflections • Can adjust pre-emphasis on chip or use pre-emphasis in FPGA.

ADCMP580 • Fast buffer amplifier with digital input. • Will remove reflections. • http://www.analog.com/static/imported-files/data_sheets/ADCMP580_581_582.pdf

Next Steps • The cable will be terminated at 100 W for eye diagram tests. • Once acceptable eye diagrams have been achieved the cable will be looped back to the FPGA for BER testing and eye diagrams for the end of the cable. • Start with 1m cable and then try longer lengths.

Spice Simulations • Simple cable model • Assumes skin loss dominant (ie dielectric losses negligible) • Model based on another cable with values scaled to our twin-ax cable. • 1 db/m attenuation • First look, so plots shown are indicative only.

3.125 Gbps 7bit PRBS 1metre cable Waveform after filter

Outlook • Started to look at eye diagrams and BER for high speed cable testing. • Need to improve test system to eliminate reflections. • Optimise eye diagrams with pre-empahsis. • Should be able to understand eye diagrams with spice simulations.