Inhoudstafel

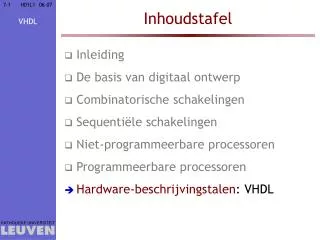

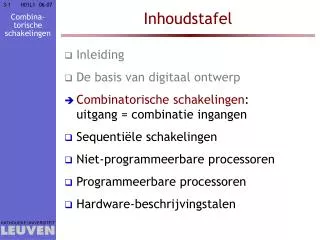

Inhoudstafel. Inleiding De basis van digitaal ontwerp Combinatorische schakelingen Sequentiële schakelingen Niet-programmeerbare processoren Programmeerbare processoren Hardware-beschrijvingstalen : VHDL. Taalgebaseerd hardware ontwerp: VHDL. Inleiding In vogelvlucht Taalelementen

Inhoudstafel

E N D

Presentation Transcript

Inhoudstafel • Inleiding • De basis van digitaal ontwerp • Combinatorische schakelingen • Sequentiële schakelingen • Niet-programmeerbare processoren • Programmeerbare processoren • Hardware-beschrijvingstalen: VHDL

Taalgebaseerd hardware ontwerp: VHDL • Inleiding • In vogelvlucht • Taalelementen • Hardware-beschrijving • Simulatie • Synthese • Inleiding • VHDL in vogelvlucht • Elementen van de VHDL-taal • Hardware-beschrijving met VHDL • Hardware-simulatie met VHDL • Hardware-synthese met VHDL

Wat is VHDL? • Inleiding • In vogelvlucht • Taalelementen • Hardware-beschrijving • Simulatie • Synthese • Acroniem VHDL: • VHDL = VHSIC Hardware Description Language • VHSIC = Very High Speed Integrated Circuit • Wat is VHDL? • Een programmeertaal om het gedrag van digitale systemen te beschrijven • Een taal om een ontwerp in te geven, bruikbaar voor • eenduidige specificatie op gedrags- & RTL-niveau • simulatie • synthese (goed bruikbaar voor RTL-niveau) • documentatie • Standaardisatie: IEEE 1076 • 1e versie: VHDL-87 • 2e versie: VHDL-93 • 3e versie: VHDL-2001

VHDL Analog and Mixed Signal • Inleiding • In vogelvlucht • Taalelementen • Hardware-beschrijving • Simulatie • Synthese • uitbreiding van (zuiver digitale) VHDL met analoge signalen • VHDL-AMS (IEEE standaard 1076.1-1999) • superset van VHDL-93 (digitaal ontwerp) • continue-tijd-model • set differentiële & algebraïsche vergelijkingen • Complex en veel minder gebruikt;voor meer info, zie • http://www.vhdl.org/vhdl-ams/ • http://www.vhdl-ams.com/

Nadelen VHDL t.o.v. schema’s • Inleiding • In vogelvlucht • Taalelementen • Hardware-beschrijving • Simulatie • Synthese • Eenvoudig te leren maar moeilijk volledig te beheersen • Conceptueel verschillend van software talen • Schijnt moeilijke syntax te hebben gebruik taalgevoelige editor met sjablonen • Nogal ‘langdradig’ (veel code nodig voor eenvoudige dingen) • Een lijst instructies is minder overzichtelijk dan een blokschema voor een mens • VHDL bevat meer mogelijkheden dan strikt noodzakelijk voor hardware synthese(bijv. specificatie tijdsgedrag voor simulatie)

Voordelen VHDL t.o.v. schema’s • Inleiding • In vogelvlucht • Taalelementen • Hardware-beschrijving • Simulatie • Synthese • Overdraagbaar over verschillende programma’s voor simulatie, synthese, analyse, verificatie, … van verschillende fabrikanten • Gemakkelijker om complexe schakelingen te beschrijven: hoger abstractieniveau met automatische synthese • Je kan ‘add’ gebruiken zonder een specifiek type van opteller te kiezen: het is de taak van het syntheseprogramma om het beste type te kiezen, rekening houdend met randvoorwaarden zoals tijdsgedrag, vermogen en kostprijs • Gemakkelijk te parametriseren (woordlengte, stapeldiepte, …) • Gemakkelijk om repetitieve structuren te beschrijven

Maar er zijn ook beperkingen • Inleiding • In vogelvlucht • Taalelementen • Hardware-beschrijving • Simulatie • Synthese • Slechts een subset van VHDL kan automatisch gesynthetiseerd worden en elke fabrikant supporteert een verschillende subset • De standaard beschrijft enkel de syntax en betekenis, niet hoe code te schrijven (codeerstijl) • Eenzelfde gedrag (bijv. MUX) kan op heel wat verschillende manieren beschreven worden, • die ieder tot een totaal andere implementatie kunnen leiden (bijv. selector of 3-state bus), • wat ook nog afhangt van het syntheseprogramma. • Je moet heel wat ervaring opdoen alvorens je aanvoelt hoe de code moet geschreven worden om tot de meest efficiënte hardware gesynthetiseerd te worden door een bepaald programma

Andere‘Hardware Description Languages’ • Inleiding • In vogelvlucht • Taalelementen • Hardware-beschrijving • Simulatie • Synthese • Verilog (IEEE 1364) • Meer verspreid in USA dan in Europa • Syntactisch verwant met C VHDL meer Ada • Beter dan VHDL?“Both languages are easy to learn and hard to master. And once you have learned one of these languages, you will have no trouble transitioning to the other.” (uit ‘VHDL Made Easy!’, D. Pellerin & D. Taylor) • PLD-talen zoals ABEL, PALASM, … • Op poortniveau voor een specifieke technologie

Taalgebaseerd hardware ontwerp: VHDL • Inleiding • In vogelvlucht • Taalelementen • Hardware-beschrijving • Simulatie • Synthese • Inleiding • VHDL in vogelvlucht • Elementen van de VHDL-taal • Hardware-beschrijving met VHDL • Hardware-simulatie met VHDL • Hardware-synthese met VHDL

Een voorbeeld Compare A[0] Compare Test A B[0] In1 A Out1 EQ A[1] B EQ In2 B[1] … Compare … A Out2 B EQ In3 A[7] B B[7] • Inleiding • In vogelvlucht • Taalelementen • Hardware-beschrijving • Simulatie • Synthese • Ontwerp schakeling ‘Test’ met • drie 8-bit ingangen (In1, In2, In3) • twee 1-bit uitgangen: • Out1 = 1 In1 In2 • Out2 = 1 In1 In3 • Hiërarchisch schema: • Schema topniveau,gebruik makend vancomponenten ‘Compare’ • Schema component‘Compare’

VHDL: entiteit & architectuur • Inleiding • In vogelvlucht • Taalelementen • Hardware-beschrijving • Simulatie • Synthese Declaratie van de entiteit ‘Compare’: ‘entity’ specificeert de interface van de schakeling (zwarte doos in een schema) -- 8-bit comparator -- entity Compare is port(A,B: in bit_vector(0 to 7); EQ: out bit); end entity Compare; architecture Behav1 of Compare is begin EQ <= '1' when (A=B) else '0'; end architecture Behav1; ‘port’ specificeert een ingangs- of uitgangssignaal ‘architecture’ beschrijft het gedrag en/of de structuur van een entiteit(het binnenste van de doos) Opmerkingen: • Een entiteit kan meerdere architecturen hebben: dit zijn verschillende implementaties van hetzelfde gedrag • Deze architectuur specificeert het gedrag op RTL-niveau; een synthese zal dit omzetten naar verbindingen op poortniveau • Een ‘port’ heeft een expliciete richting en is een bit(vector)

VHDL: component & instantiatie • Inleiding • In vogelvlucht • Taalelementen • Hardware-beschrijving • Simulatie • Synthese Specificatie van het topniveau ‘Test’: -- Component Test met 2 comparatoren -- entity Test is port(In1,In2,In3: in bit_vector(0 to 7); Out1,Out2: out bit); end entity Test; architecture Struct1 of Test is component Comparator is port(X,Y: in bit_vector(0 to 7); Z: out bit); end component Comparator; begin Compare1: component Comparator port map (In1,In2,Out1); Compare2: component Comparator port map (In1,In3,Out2); end architecture Struct1; Virtuele component: laat onafhankelijke ontwikkeling van alle hiërarchische niveaus toe.‘Comparator’ kan later aan ‘Compare’ gekoppeld worden Twee instantiaties van dezelfde component met zijn signaalbindingen Opmerkingen: • Deze architectuur beschrijft de structuur, nl. hoe deze entiteit opgebouwd is als verbonden componenten van lager niveau • De twee componenten ‘Comparator’ werken tegelijkertijd!

VHDL: configuratie • Inleiding • In vogelvlucht • Taalelementen • Hardware-beschrijving • Simulatie • Synthese • Hoe wordt aangegeven welke architectuur van een entiteit gebruikt moet worden? • Hoe componenten aan entiteiten koppelen? -- Configuratie: definieer koppeling component met een -- bepaalde architectuur van een entiteit configuration Build1 of Test is for Struct1 for Compare1: Comparator use entity Compare(Behav1) port map (A => X, B => Y, EQ => Z); end for; for Compare2: Comparator use entity Compare(Behav1) port map (A => X, B => Y, EQ => Z); end for; end for; end configuration Build1; Opmerking: • ‘configuration’ komt in software overeen met ‘linking’

Vergelijking met een traditionele taal (zoals C++, Java, …) Functie-interface: argumenten = ingangen resultaat = uitgang • Inleiding • In vogelvlucht • Taalelementen • Hardware-beschrijving • Simulatie • Synthese // 8-bit comparator boolean Compare(int A, int B) { return (A == B); } Gedragsbeschrijving van de functie // Topniveau Test main() { int In1, In2, In3; boolean Out1, Out2; cin >> In1 >> In2 >> In3; Out1 = Compare(In1, In2); Out2 = Compare(In1, In3); cout << Out1 << Out2; } 2 oproepen van de functie ‘Compare’ met de gekoppelde argumenten Opmerkingen: • Functie-argumenten zijn altijd ingangen • Slechts 1 gedragsbeschrijving per functie mogelijk • De twee ‘Compare’-functies worden sequentieel uitgevoerd • ‘main’ wordt éénmaal uitgevoerd en stopt dan

Verschil met traditionele talen • Inleiding • In vogelvlucht • Taalelementen • Hardware-beschrijving • Simulatie • Synthese • Datatypes • Nood aan typische hardware-types: bitvectoren, getallen met een arbitraire grootte, getallen met vaste komma • Gelijktijdigheid (‘concurrency’) • Alle hardwarecomponenten werken in parallel • Tijdsconcept • Alle componenten werken continu:hardware stopt nooit! • Voor simulatie is een koppeling met het reële tijdsgedrag van componenten nodig

Taalgebaseerd hardware ontwerp: VHDL • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Inleiding • VHDL in vogelvlucht • Elementen van de VHDL-taal • Lexicale elementen (woordenschat) • Data-objecten & -types • Bewerkingen • Controle-uitdrukkingen • Subprogramma’s • Bibliotheken • Hardware-beschrijving met VHDL • Hardware-simulatie met VHDL • Hardware-synthese met VHDL

Lexicale elementen • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Commentaar: van ‘--’ tot einde lijn • ‘Identifier’ (of naam) • reeks van alphanumerische karakters of niet-opeenvolgende ‘_’, die start met een letter & niet eindigt met ‘_’: “Next_value_0” • Geen verschil hoofdletters / kleine letters! • Getal • ‘integer literal’: geheel getal “1480”‘real literal’: fractioneel getal “1480.0” • Beide kunnen exponentieel “148E1” • ‘_’ wordt genegeerd “1_480” • Niet-decimale basis : base#literal#exp253.5 = 16#FD.8#2#1#E10 = 16#4#E2

Lexicale elementen • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Karakter • ‘character literal’ = één karakter tussen enkele aanhalingstekens: 'a' 'A' ''' • Karakterreeks (‘string’) • ‘string literal’ = reeks karakters tussen dubbele aanhalingstekens: "A string" • ‘""’ om ‘"’ in een string te krijgen:"""Quote it"", she said." • Bitreeks (‘bit string’) • ‘bit string literal’ = reeks bits, voorgesteld door een reeks cijfers voorafgegaan door een basisspecificatie (‘B’, ‘O’, of ‘X’) :O"12" = b"001_010"X"a" = B"1010"

Taalgebaseerd hardware ontwerp: VHDL • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Inleiding • VHDL in vogelvlucht • Elementen van de VHDL-taal • Lexicale elementen • Data-objecten & -types • VHDL-objecten • VHDL-types • Attributen • Bewerkingen • Controle-uitdrukkingen • Subprogramma’s • Bibliotheken • Hardware-beschrijving met VHDL • Hardware-simulatie met VHDL • Hardware-synthese met VHDL

VHDL-objecten • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • benoemd item dat een waarde van een specifiek type heeft • Constante • maakt programma meer verstaanbaar • Variabele • bevat tussenresultaten zonder fysische betekenis • geen verband met een ASM-variabele! • Signaal • draad, (interne) verbinding • golfvorm, zoals zichtbaar tijdens een simulatie • Bestand

Declaratie VHDL-object namen gescheiden door een komma • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Constanteconstantname(s): (sub)type := expression; • constant num_bytes: integer := 4;constant num_bits: integer := 8 * num_bytes; • Variabelevariablename(s): (sub)type[:= expression]; • variable cnt, index: integer := 0; opm.: default-waarde = eerste (linkse) waarde(bijv. kleinst voorstelbaar geheel getal) • Signaalsignalname(s): (sub)type[:= expression]; • signal a, b: bit; gereserveerd woord initiële waarde

Toekenning aan VHDL-object a y b • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Variabelenname := expression; • index := index + 1; • Signalenname <= waveform; • Eenvoudige golfvorm (synthese) : expression • y <= a and b; • Complexe golfvorm (simulatie) :[delay_mechanism] expression[aftertime] [, expression[aftertime]]… • line_out <= transport line_in after 100 ps;pulse <= '1', '0' after T_pw;

Taalgebaseerd hardware ontwerp: VHDL • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • scalair • matrix • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Inleiding • VHDL in vogelvlucht • Elementen van de VHDL-taal • Lexicale elementen • Data-objecten & -types • VHDL-objecten • VHDL-types • Attributen • Bewerkingen • Controle-uitdrukkingen • Subprogramma’s • Bibliotheken • Hardware-beschrijving met VHDL • Hardware-simulatie met VHDL • Hardware-synthese met VHDL

VHDL: (sub)types • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • scalair • matrix • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • VHDL-types • Scalaire types : set waarden • Samengestelde types : verzameling sets • ‘Access’ types : ‘pointers’ voor gelinkte lijsten • Bestandstypes • Declaratie typetypenameistype_definition; • type int_8 is range -128 to 127; • Declaratie subtype= beperkte set waarden van basistypesubtypenameisscalar_(sub)type[rangeexpression (down)toexpression]; • subtype nat_8 is int_8 range 0 to 127;

Taalgebaseerd hardware ontwerp: VHDL • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • scalair • matrix • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Inleiding • VHDL in vogelvlucht • Elementen van de VHDL-taal • Lexicale elementen • Data-objecten & -types • VHDL-objecten • VHDL-types • Scalaire types • Samengestelde types • Attributen • Bewerkingen • Controle-uitdrukkingen • Subprogramma’s • Bibliotheken • Hardware-beschrijving met VHDL • Hardware-simulatie met VHDL • Hardware-synthese met VHDL

Declaraties van scalaire types • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • scalair • matrix • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Discrete types • ‘Integer’ types (gehele getallen)rangeinteger_expression (down)tointeger_expression • type mem_address is range 65535 downto 0; • ‘Enumeration’ types (opsommingen)(name_or_charliteral[, name_or_charliteral]…) • type FSM_state is (reset, wait, input, calculate, output);type tri_val is ('0', '1', 'Z'); • Komma-types • rangereal_expression (down)toreal_expression • type probability is range 0.0 to 1.0; • Fysische types

Declaraties van scalaire types Primaire eenheid Metrische eenheden Engelse eenheden • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • scalair • matrix • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Fysische typesrangeexpression (down)toexpressionunitsidentifier;[identifier = physical_literal;]…end units • type length is range 0 to 1E9units um; mm = 1000 um; m = 1000 mm; km = 1000 m; mil = 254 um; inch = 1000 mil; foot = 12 inch; yard = 3 foot;end units; Primaire eenheid: nauwkeurigheid Secundaire eenheden

Voorgedefinieerde scalaire types • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • scalair • matrix • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Opsommingen • type bit is ('0','1'); • type boolean is (false, true); • type character is (ASCII set); • namen voor niet-afdrukbare controlekaraktersbijv. nul, cr, lf, esc, del • type severity_level is (note, warning, error, failure); • Gehele getallen • type integer is rangeimplementation_defined; • bereik minstens van −231+1 tot +231−1 • subtype natural is integerrange 0 to integer'high; • subtype positive is integerrange 1 to integer'high;

Voorgedefinieerde scalaire types • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • scalair • matrix • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Komma-types • type real is rangeimplementation_defined; • bereik minstens IEEE 32-bit enkelvoudige precisie • Fysische types • type time is rangeimplementation_definedunits fs; ps = 1000 fs; ns = 1000 ps; us = 1000 ns; ms = 1000 us; sec = 1000 ms; min = 60 sec; hr = 60 min;end units;

IEEE 1164 ‘Standard logic’ • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • scalair • matrix • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese Meer dan ‘0’ en ‘1’ nodig voor logische signalen, daarom definieert IEEE standaard 1164 signalen met 9 waarden.Gebruik altijd deze i.p.v. ‘bit’ voor echte toepassingen! library IEEE; use IEEE.Std_logic_1164.all;type std_ulogic is ( 'U', -- niet geïnitialiseerd, bijv. bij opstarten 'X', -- sterk aangestuurd ongekend -- bijv. na schending set-up '0', -- sterk aangestuurd logisch 0 '1', -- sterk aangestuurd logisch 1 'Z', -- hoog-impedant -- m.a.w. niet aangestuurd 'W', -- zwak aangestuurd ongekend 'L', -- zwak aangestuurd logisch 0 'H', -- zwak aangestuurd logisch 1 '-'); -- don’t caretype std_logic is resolved std_ulogic;subtype X01 is resolved std_ulogic range 'X' to '1'; actieve aansturing resistieve aansturing

Taalgebaseerd hardware ontwerp: VHDL • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • scalair • matrix • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Inleiding • VHDL in vogelvlucht • Elementen van de VHDL-taal • Lexicale elementen • Data-objecten & -types • VHDL-objecten • VHDL-types • Scalaire types • Samengestelde types • Attributen • Bewerkingen • Controle-uitdrukkingen • Subprogramma’s • Bibliotheken • Hardware-beschrijving met VHDL • Hardware-simulatie met VHDL • Hardware-synthese met VHDL

Declaraties samengestelde types • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • scalair • matrix • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese multidimensioneel • ‘Array’ types (matrices) • Begrensd (‘constrained’): grenzen indices vastarray (range[, range]…) of(sub)typemet range ofwel een discreet subtype ofwel expression (down)toexpression • type word is array (15 downto 0) of bit; • type next_state is array (FSM_state, bit) of FSM_state;variable next: next_state;next(calculate, '1') := output; • Onbegrensd : grenzen niet bepaaldarray ((sub)typerange <>[, (sub)typerange <>]…) of(sub)type • type sample is array (natural range <>) of integer;subtype buf_type is sample(0 to 255); variable sample_buf: sample(0 to 63); • ‘Record’ types LSB, bit 0 MSB

Voorgedefinieerdesamengestelde types • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • scalair • matrix • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Onbegrensde matrices • type string is array (positive range<>) of character; • constant Error_message: string := "Unknown error: ask for help"; • type bit_vector isarray (natural range<>) of bit; • constant State1: bit_vector(4 downto 0) := "00100"; • Onbegrensde matrices in IEEE 1164 • type std_[u]logic_vector isarray (natural range<>) of std_[u]logic;

Toekenning aan een matrix signal Down: std_logic_vector (3 downto 0); signal Up: std_logic_vector (0 to 3); Up <= Down; Welke van de twee volgende interpretaties is correct? Up(0) Up(1) Up(2) Up(3) Down(3) Down(2) Down(1) Down(0) Up(0) Up(1) Up(2) Up(3) Down(0) Down(1) Down(2) Down(3) of • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • scalair • matrix • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Matrices kunnen aan mekaar toegekend worden als ze dezelfde dimensies en grootte hebben • Correspondentie via positie, niet via index!

‘Array literal’ • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • scalair • matrix • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • (Bit)string literal • variable w: word := "1010000101111111";variable w: word := x"A17F"; • Matrixgeheel (‘array aggregate’) • Associatie volgens positie(expression [, expression]…) • type point is array (1 to 3) of integer;variable p: point := (4, 5, 5); • Associatie volgens naam(choice [| choice]… => expression[, choice [| choice]… => expression]…)metchoice ofwel een uitdrukking, een discreet bereik of others • variable p: point := (3 => 5, 1 => 4, 2 => 5);variable p: point := (1 => 4, 2 | 3 => 5);variable p: point := (1 => 4, 2 to 3 => 5);variable p: point := (1 => 4, others => 5); • sample_buf := (others => 0); init onafh. van grootte

Matrixdeel (‘slice’) • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • scalair • matrix • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • subset van opeenvolgende matrixelementen • Zorg ervoor dat de richting (to of downto) dezelfde is als in de declaratie! • Matrix begrenzen met een subtype-definitie • subtype halfword is bit_vector(0 to 15); • Toekenning aan een stuk van een matrix • signal Bus: std_logic_vector (7 downto 0);signal A: std_logic_vector (0 to 3);Bus <= A;Bus(0 to 3) <= A;Bus(3 downto 0) <= A;Bus(5 downto 4) <= A(0 to 1); verschillende groottes richting Bus verschilt van declaratie OK! Bus(3) <= A(0) OK! Bus(5) <= A(0)

Concatenatie van(ééndimensionale) matrices • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • scalair • matrix • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • samenvoeging door draden te bundelen • signal Byte_bus: bit_vector(7 downto 0); • signal Nibble_busA, Nibble_busB: bit_vector(3 downto 0); • Byte_bus <= Nibble_busA & Nibble_busB; Nibble_busA(3) Nibble_busA(2) Nibble_busA(1) Nibble_busA(0) Byte_bus(7) Byte_bus(6) Byte_bus(5) Byte_bus(4) Byte_bus(3) Byte_bus(2) Byte_bus(1) Byte_bus(0) Nibble_busB(3) Nibble_busB(2) Nibble_busB(1) Nibble_busB(0)

Taalgebaseerd hardware ontwerp: VHDL • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Inleiding • VHDL in vogelvlucht • Elementen van de VHDL-taal • Lexicale elementen • Data-objecten & -types • VHDL-objecten • VHDL-types • Attributen • Bewerkingen • Controle-uitdrukkingen • Subprogramma’s • Bibliotheken • Hardware-beschrijving met VHDL • Hardware-simulatie met VHDL • Hardware-synthese met VHDL

Attributen • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • informatie over objecten & types • Voorbeelden van voorgedefinieerde attributen • van scalaire types • T'left : eerste waarde van T • T'low : kleinste waarde van T • T'pos(x) : positie van x in T • van matrixtypes & -objecten • A'range[(n)] : indexbereik van dimensie n • A'length[(n)] : grootte van indexbereik • A'left[(n)] : eerste waarde in indexbereik • van signalen • S'event : true als er een ‘event’ was opS in de huidige simulatiecyclus • S'last_event : tijd sinds laatste ‘event’ op S

Attributen gedefinieerddoor de gebruiker • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • objecten • types • attributen • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • toevoegen beperkingen en informatie buiten de structuur en het gedrag • Declaratie van een attribuutattributename : sub(type); • attribute pin_number : positive;attribute encoding : bit_vector; • Specificatie van een attribuut attributename of name(s) : class is expression; • attribute pin_number of EN_1, EN_2: signal is 14;attribute encoding of state1: literal is b"0000";

Taalgebaseerd hardware ontwerp: VHDL • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Inleiding • VHDL in vogelvlucht • Elementen van de VHDL-taal • Lexicale elementen • Data-objecten & -types • Bewerkingen:logisch, relationeel, aritmetisch & schuiven • Controle-uitdrukkingen • Subprogramma’s • Bibliotheken • Hardware-beschrijving met VHDL • Hardware-simulatie met VHDL • Hardware-synthese met VHDL

Logische bewerkingen • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Lijst van logische operatoren:not, and, or, xor, nand, nor, xnor • Prioriteit: • ‘not’ heeft de hoogste prioriteit • Alle andere hebben gelijke prioriteit lager dan ‘not’ • Gedefinieerd voor de datatypes: bit[_vector], boolean, std_[u]logic[_vector] • Kan op matrices van dezelfde grootte • Bewerkingen gebeuren telkens op elementen met overeenkomende posities • Resultaat is een (matrix van) boolean niet in VHDL-87

Vergelijkingen • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Lijst van relationele operatoren:<, <=, =>, >, =, /= • Beide operanden moeten van hetzelfde type zijn • Resultaat is een boolean • Kan op matrices, zelfs van verschillende grootte • Algoritme: • aligneer de matrices op linkerelement • vergelijk element per element, van links naar rechts • vergelijk maximaal zoveel elementen als er in de kleinste matrix aanwezig zijn • Daarom zijn de volgende vergelijkingen waar: • "1110" > "10111" • "1110" = "11101" • Dit werkt dus op bitvectoren van gelijke lengte alsof het positieve getallen waren

Aritmetische bewerkingen • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Lijst van aritmetische operatoren: +, −, *, /,** (exponent), abs (absolute waarde), mod (modulus), rem (rest) • Gedefinieerd voor • datatypes integer en real (behalve mod en rem), maar niet op bitvectoren • Gebruik ‘overloading’ voor bitvectoren(niet standaard!) • fysische datatypes (enkel +, −) • Operanden moeten van hetzelfde type zijn, maar verschillende bereiken zijn toegelaten • Een variabele van het fysische type (bijv. time) kan ook vermenigvuldigd worden met (of gedeeld worden door) een integer of een real; het resultaat blijft van het fysische type

Schuifoperaties • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Lijst van schuifoperatoren (niet in VHDL-87): sll (‘shift-left logical’), srl,sla (‘shift-left arithmetic’), sra,rol (‘rotate left’), ror • De eerste operand is een vector van bits of van booleans • De tweede operand is een integer; als deze negatief is, schuif in de tegengestelde richting • Het resultaat is van hetzelfde type als de eerste operand • Voorbeelden: • B"10001010" sll 3 = B"01010000"B"10001010" sll -2 = B"00100010"B"10001010" sra 3 = B"11110001"B"10001010" ror 3 = B"01010001"

Taalgebaseerd hardware ontwerp: VHDL • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Inleiding • VHDL in vogelvlucht • Elementen van de VHDL-taal • Lexicale elementen • Data-objecten & -types • Bewerkingen • Controle-uitdrukkingen:conditionele uitdrukkingen & lussen • Subprogramma’s • Bibliotheken • Hardware-beschrijving met VHDL • Hardware-simulatie met VHDL • Hardware-synthese met VHDL

Conditionele uitdrukkingen • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Uitdrukking “if” ifboolean_expressionthenstatement(s)[elsifboolean_expressionthenstatement(s)]…[elsestatement(s)]end if; • Opmerking: • Ingebouwde prioriteit: de eerste voorwaarde die waar is bepaalt welke statement(s) uitgevoerd worden

Conditionele uitdrukkingen • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Uitdrukking “case” caseexpressionis whenchoice(s)=> statement(s) [whenchoice(s)=> statement(s)]…end case; • case x iswhen 0 to 4 => y <= 'Z';when 5 => y <= '1';when 7 | 9 => y <= '0';when others => null;end case; • Voorwaarden: • Alle mogelijke waarden moeten exact eenmaal gespecificeerd worden als choice • De waarden zijn van hetzelfde type als expression • De waarden zijn constant en gekend op het moment van ontwerp slechts eenmaal geëvalueerd doe niets

Lussen • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • Oneindige lusloopstatement(s)end loop; • Oneindige lussen zijn typisch voor hardware!-- 4-bit teller met uitgang “count”val := 0;loop count <= val;wait until clk = '1' ; val := (val + 1) mod 16;end loop; • “exit”-uitdrukkingexit[whenboolean_expression]; • “next”-uitdrukkingnext[whenboolean_expression]; wacht totclk'1' wordt or reset = '1'exit when reset = '1';

Lussen • Inleiding • In vogelvlucht • Taalelementen • Lexicaal • Data • Bewerkingen • Controle • Sub-programma's • Bibliotheken • Hardware-beschrijving • Simulatie • Synthese • “while”-luswhileboolean_expressionloopstatement(s)end loop; • “for”-lusfornameinrangeloopstatement(s)end loop; • De lusvariabele name • moet niet gedeclareerd worden • kan alleen binnen de lus gebruikt worden • Enkele voorbeelden van range: • for i in 0 to 3 loop… • for i in an_array'range loop… • for state in FSM_state loop …