VHDL Implementation for the SRC ALU

VHDL Implementation for the SRC ALU. Edgar Arce Miguel González Miguel Padilla José F. Ocasio December 15, 2004. Introduction Overview Adder Register B interface ALU_hi Lowalu (1 bit). Lowalu(10 bits) ALU ALU_System ALU_ADC Conclusions References Acknowledgements. Outline.

VHDL Implementation for the SRC ALU

E N D

Presentation Transcript

VHDL Implementation for the SRC ALU Edgar Arce Miguel González Miguel Padilla José F. Ocasio December 15, 2004

Introduction Overview Adder Register B interface ALU_hi Lowalu (1 bit) Lowalu(10 bits) ALU ALU_System ALU_ADC Conclusions References Acknowledgements Outline

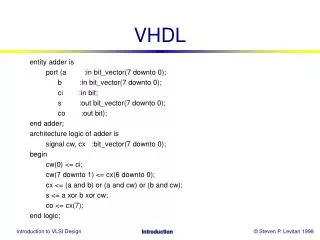

Introduction • Simple Risc Computer - architecture designed specially for educational purposes • Simple structure • 32 bit CPU • For INEL 4215 purposes, it has been simplified to 8 bits • Simplified ALU executes SRC operations for 10 bits inputs • Next - an implementation for the 10 bit SRC ALU with an additional instruction called ADC

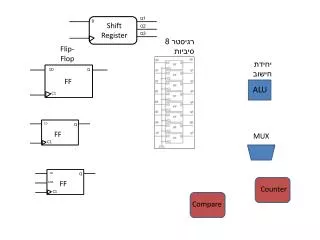

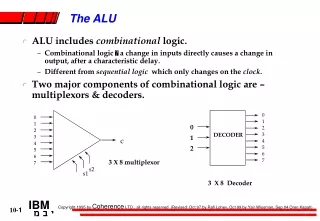

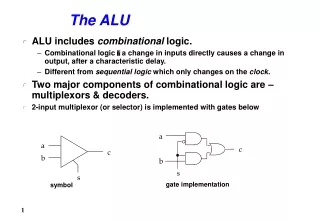

Overview General diagram of the SRC ALU

Conclusions • Instruction C = B needs no additional circuitry to be implemented, it is made by no activating any signal. • ALU of 10bits instead of 8bits because of Program Counter. • Implemented ADDER not a ADDER_SUBSRACTOR, because an additional module is needed to implement a NOT function. • When a SHIFT function is called the ALU only shifts once because the Control Unit handles the counter of it.

References • http://www.gmvhdl.com/VHDL.html • http://www.isee.zju.edu.cn/hmx/asiclab2000/lab3help/tutvhdl/tutvhdl.htm • http://www.wearcam.org/ece385/lectureflipflops/flipflops/ • Computer Systems Design and Architecture, 2/E , Heuring, V. P. y Jordan, H. F., Prentice Hall, 2004.

Acknowledgements • To God. • Always helpful Google. • Buhos Society • To the Buho VHDL Sensei Marcos Mejias. • To the lobby’s benches for giving us a place to sleep. • To Chori for supplying us with healthy food at 3:00am.