Advancements in CAD Technologies for Efficient Mapping of Macro Blocks

150 likes | 293 Vues

This document presents a comprehensive outline of a 2013 CAD contest entry focused on technology mapping for macro blocks. The team, WCYLab-Bach, explores problem formulation and introduces innovative concepts in input parsing and mapping algorithms. Key areas include logical and arithmetic operations through various libraries, with an emphasis on multi-PO library strategies. The implementation phase and alpha testing of the mapping algorithms are also discussed, highlighting the potential for future enhancements in CAD technologies.

Advancements in CAD Technologies for Efficient Mapping of Macro Blocks

E N D

Presentation Transcript

2013 CAD Contest Technology Mapping for Macro Blocks Team: WCYLab-Bach Date: 2013/6/24

Outline • Problem Formulation • Main Idea

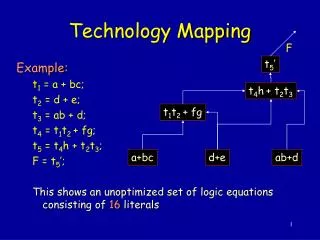

Input Parser ABC D D.blif Mapping ABC D’.blif D’.v Library VTR L.blif

Main idea – Library (arithmetic op) (0, 1, a) Library random, learning L1 L3 L2 NPI < PImax

Main idea – Library (arithmetic op) Adder A a1,b1 Adder 0 0 0 B a2,b2 0 0 0

Main idea – Library (about multi-PO) Library Library

Main idea(New) Library Library Library Library X X X X X

Main idea(New) Library Library Library Library X X X X X (0, 1, a) (0, 1, a) (0, 1, a) (0, 1, a)

Main idea(New) Library Library Library X X X X X (0, 1, a) (0, 1, a) (0, 1, a) (0, 1, a)

Output Parser ABC D D.blif ABC - mapping Mapping D’.blif D’.v Library VTR L.blif

Future work • Alpha test – done • Implementation