Memory Management

Memory Management. Computer Studies (AL). Content. Overview of memory management Logical and physical address spaces Swapping Paging Segmentation. Introduction. A program must be brought into memory and placed within a process to be executed.

Memory Management

E N D

Presentation Transcript

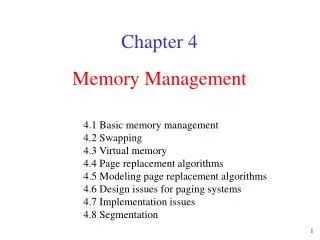

Memory Management Computer Studies (AL)

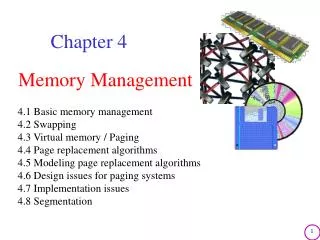

Content • Overview of memory management • Logical and physical address spaces • Swapping • Paging • Segmentation

Introduction • A program must be brought into memory and placed within a process to be executed. • As the process is executed, it access instructions and data from memory. • If the process can be moved during its execution from one memory segment to another: • Binding must be delayed until run time • This is called execution-time addressing-binding scheme • Special hardware must be available for this scheme.

Logical and physical address Space • An address generated by the CPU is referred to as a logical address. • The address seen by the memory unit (I.e. the one loaded into the memory address register) is referred to as a physical address. • The execution-time addressing binding scheme results in an environment where the logical and physical address differ.

Logical and physical address Space • We usually refer to the logical address as a virtual address. • The set of all logical address generated by a program is referred to as a logical address space. • The set of all physical address corresponding to these logical addresses is referred to physical address space.

Memory-management unit (MMU) • The run-time mapping from virtual to physical address is done by MMU, which is a hardware device. • The simplest MMU is to make use of a relocation register. • The user only deals with logical address. MMU CPU Memory Relocation register : 14000 Physical address 14346 Logical address 346

Swapping • A process needs to be executed. • A process may be swapped temporarily out of memory to a backing store. • Later it will be brought back into memory for continued execution.

Example of swapping • Multiprogramming environment with a round-robin CPU-scheduling. • When a time quantum expires, the OS will start to swap out the process that just finished, and to swap into another process to the memory space that has been freed. • The CPU scheduler will allocate a time slice to some other process in memory. Process 1Process 2… OS Swap out MEM Swap in User Space

Swapping details • If execution-time binding is being used, then it is possible to swap a process into a different memory space. • Because the physical addresses are computed during run-time. • The backing store is commonly a fast disk and must be large enough to accommodate copies of all memory images for all users.

Swapping details • A more detailed description of a typical situation which requires swapping. • The OS maintains a ready queue consisting of all process whose memory images are either in memory or on the backing store. • Whenever the CPU scheduler decides to execute a process, it calls the dispatcher. • The dispatcher checks to see whether the next process in the queue is in memory. • If the process is not, and there is no free memory region, the dispatcher swaps in the desired process. • It then reloads registers as normal and transfer control to the selected process.

Swapping details • The time quantum in round-robin CPU scheduling should be substantially larger than swap time (transfer time) • Unix and windows has its own modified version of swapping.

Paging • Physical memory is broken into fixed-sized blocks called frames. • Logical memory of process is broken into blocks of the same size called pages. • The pages of a process are loaded into available frames for execution. • The physical address space of a process is noncontiguous. (非鄰接的)

Paging Frame Number Page0 Page1 Page2 Page3 Logical Memory Page table Physical Memory

Paging • Every address generated by the CPU is divided into two parts: • A page number (p) • A page offset (d) • The page number is used as an index into a page table. • The page table contains the base address of each page in physical memory. • The base address is combined with the page offset to define the physical memory address.

Paging Physical address Logical address CPU p Physical memory Page table

Paging • The typical page size is a power of 2 varying between 512 bytes and 8192 bytes per page. • Consider a m-bit logical address. Suppose a page size is 2 to power n bytes. • The n low-order bits designate the page offset. • The high-order m – n bits designate the page number. (where p is an index into the page table and d is the displacement within the page.) Page number Page offset m-n n

Frame number Paging example • Consider the following example of a page size of 4 bytes: Page Number Page table Logical memory

Paging • Paging itself is a form of dynamic relocation. • Page frames are allocated as units • The last frame allocated may not be completely full. • E.g. a process of 72766 bytes would need 35 pages plus 1086 bytes. • (Assume 1 page has 2048bytes) • *Internal fragmentation occurs. • It would be allocated 36 frames.

Page allocation • When a process arrives, its size, expressed in pages is examined. • If it requires n pages, then n available frames are allocated to this process. • The frame number is put in the page table for this process. • The OS also maintains a frame table indicating whether a frame is free or allocated.

Page allocation Frame table memory Frame table memory Page table Before allocation After allocation

Hardware Support for the page table • Implementation of the page table can be done in several ways. • 1. Using Dedicated Registers • Use a set of dedicated registers • These registers make the paging translation efficient • DEC PDP-11: it uses 8 registers for paging • Disadv: It doesn’t support large page table used in most modern computer.

Hardware support for the page table • 2. Using memory • The page table is kept in memory • A page-table base register (PTBR) is used to point to the page table. • IF we want to access a location, we first index into the page table, using the value in the PRBR offset by the page number. • This task requires one memory access • The frame number obtained is combined with the page offset to produce the actual address • The desired place in memory can then be accessed. • This also requires one memory access. • As a result, 2 memory access are needed to access a byte. • Disadv: Each memory access is slowed by a factor of 2.

Hardware support for the page table • 3. Using associative Registers • Use a special and fast-lookupm hardware cache called associative registers ro translation look-aside buffers (TLBs) • Each register consists of two parts: a key and a value

Details of TLBs • The mechanism of TLBs • Associative registers can compare with all keys simultaneously • If an item is found, the corresponding value field is output. • The search is fast due to hardware. • The page table is stored in memory • TLBs are used to store some of the page table entries.

TLBs Logical address Physicalmemory CPU Page number Frame number Physical address TLB hits TLB miss TLB Page table

Mechanism of TLB • When logical address is generated by the CPU, its page number is presented to the associative registers. • If the page number is found, its frame number is used to access memory. • If the page number is not found, • A memory reference to the page table must be made. • The corresponding entry is added to the TLB. • If the TLB is already full of entries, the OS must select one for replacement.

Mechanism of TLBs • The % of times that a page number is found in TLBs is called the hit ratio. • An 80% hot ratio means that we find the desired page number in TLBs 80 percent of the time. • If it takes 20 nsec to search the TLB and 100 nsec to access memory • If the page number is in TLB, then a memory access takes 120 nsec. • If the page number is not in TLB, then it must first access memory for the page table, and then access the desired byte in memory, for a total of 220 nsec.

effective memory-access time • Find the effective memory-access time: • =hx120 + (1-h) x 220 • Where h is the hit ratio • Example: if hit ratio is 80% • EAT = 0.8 x 120 + 0.2 x 220 = 140 nsec

Additional Notes:Cache operation • The previous operations is used to find the physical address (real) from logical address (virtual), which is called TLB operation. • After finding the physical address, the memory cache is consulted see if the block containing that world is present, which is called cache operation. • If so, it is returned to the CPU directly. • If not, the word is retrieve from main memory, or harddisk (if the required page is not in memory)

Segmentation • Segmentation allows the programmer to view memory as consisting of multiple address spaces or segments. • Memory references consist of a <segment number, offset> form of address. • Segments are of variable size, and each segment may be divided into pages.

Segmentation • Typically, the programmer or the compiler/OS will assign programs and data to different segments. Each segment may be assigned access and usage rights.

Advantages of segmentation • It simplifies the handling of growing data structures. • If the programmer does not know ahead of time how large a particular data structure will become, it is not necessary to guess. The data structure can be assigned its own segment, and the operating system will expand or shrink the segment as needed.

Advantages of segmentation • 2. It allows programs to be altered and recompiled independently, without requiring that an entire set of programs be relinked and reloaded. Again, this is accomplished using multiple segments.

Advantages of segmentation • 3. It lends itself to sharing among processes. • A programmer can place a utility program or a useful table of data in a segment that can be addressed by other processes.

Advantages of segmentation • 4. It lends itself to protection. • Because a segment can be constructed to contain a well-defined set of programs or data, the programmer or a system administrator can assign access privileges in a convenient fashion.

Pentium II Memory address-translation mechanism Logical address Linear address Physical Address PageDirectory SegmentTable Page Table Paging Main Memory Segmentation Note: The address translation mechanism for segment involves mapping a virtual address into what is referred to as a linear address When segmentation is not in use, linear addresses are used in programs.

Why paging? • Why paging? • Where is the page table located?