Reconfigurable Processing Module (RPM)

This presentation provides an in-depth overview of the Reconfigurable Processing Module (RPM), a core component designed for hosting reconfigurable FPGA fabric. It details the RPM architecture, including block diagrams, on-chip network interfaces, and system modeling. We explore various applications, including soft processors and custom hardware solutions. Challenges faced during development and the current status of the project are discussed, along with options for enhancing performance through robust architectural alternatives.

Reconfigurable Processing Module (RPM)

E N D

Presentation Transcript

Reconfigurable Processing Module(RPM) Kevin Somervill1 (kevin.m.somervill@nasa.gov) Dr. Robert Hodson1 (robert.f.hodson@nasa.gov) Dr. John Williams2 (jwilliams@itee.uq.edu.au) Dr. Robert Jones3 (robert.jones@akspace.com) 1 NASA Langley Research Center 2 The University of Queensland, Australia 3 ASRC Aerospace Corp. 125/MAPLD'05

Presentation Topics • RSC Platform Architectural Overview • RPM Architecture Block Diagram • Interface On-Chip Network Diagram • Example Applications • Soft processor Based • Custom Hardware • Major Components • System Modeling • Embedded Computing (MicroblazeTM) • Development Challenges and Issues • Current Status 125/MAPLD'05

RSC Platform Architectural Overview • Collection of one or more modular stacks of computing elements • RPM is core reconfigurable component hosting reconfigurable FPGA fabric 125/MAPLD'05

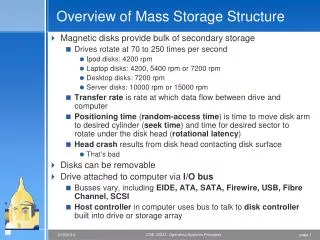

Reconfigurable Application FPGA (Xilinx 4VFX60) Serial Port RS422 Serial Port RS232 Serial XCVR 2.5Gbps RS232 SMAP Configuration Manager SDRAM 512 MB Flash User I/O Serial I/F Serial I/F Memory I/F Interface FPGA (Actel AX2000) NIC Bus Arbiter Proto: 2V3000 *Proto Only RPM Architecture Block Diagram User Logic Configuration Memory SLiP I/F Dual Fast Simplex Links 66MHz 8/16-bit (24,16) EDAC66 MHz SLout SLin SLiP I/F On Chip Bus PCI Controller PCI I/F 3.3V PCI 33MHz 32/64-bit 125/MAPLD'05

I/F Logic I/F Logic I/F Logic I/F Logic (Actel)I/F FPGA NIC Bus Arbiter On Chip Network Diagram Configuration Manager SLiP I/F Controller On Chip Bus Memory Controller PCI Controller • Alternatives and issues • Crossbar logic – potential enhancement to first pass architecture if greater bandwidth is required • RapidIO – an attractive possibility, but considered to be too costly and complex for most applications. • Hypertransport – Similar to RapidIO, it was considered to be excessively more than needed. 125/MAPLD'05

Application FPGA (Xilinx) High Speed Serial I/F Cache Controller Configuration I/F SLiP I/F SDRAM Serial I/F Memory I/F Flash I/F FPGA (Actel) NIC Bus Arbiter Example Custom Hardware Application I/O Processor FSL uP OPB Timer Interrupt Controller Application Processor uP LMB On-Chip PeripheralBus (24,16) EDAC66 MHz LMB On Chip Bus PCI I/F 3.3V PCI 33 MHz 32/64 bits 125/MAPLD'05

Application FPGA (Xilinx) High Speed Serial I/F Configuration I/F SLiP I/F SDRAM Serial I/F Memory I/F Flash I/F FPGA (Actel) NIC Bus Arbiter Example Custom Hardware Application FFT/ Convolution Engine Data Filter FUZZY Logic Controller Data Packetizer (24,16) EDAC66 MHz On Chip Bus PCI I/F 3.3V PCI 33 MHz 32/64 bits 125/MAPLD'05

Major Components High Speed Serial Interface • Components • AX2000 (CCGA624) • Actel • 4VFX60 (CF1144) • Xilinx • 3D-Plus Stacked SDRAM (512MB) • Flash (8MB at least) • TLK2711 MGT • Texas Instrument • Voltage Regulation • Prototype will use XC2V3000 instead of the AX2000 Voltage Regulation Application FPGA (V4FX60) External I/O Interface FPGA (AX2000) Memory Subsystem PCI-104 Connector PCI-104 Extension 125/MAPLD'05

Systems Modeling • Development support with formal modeling • Petri nets providing performability modeling which considers both reliability and performance aspects in a unified model • Petri nets provides mathematically based rigorous approach to system evaluation and development • Petri nets converted to SystemC models • To serve as faster lower level system simulation models • Provides step wise refinement of the model towards RTL while providing the eventual test bench for the final VHDL • SystemC model provides simplified path to software evaluation for prospective applications 125/MAPLD'05

Embedded Processing • Primary target microprocessor is the MicroblazeTM processor. • Leverage work done with XRTC • Design mitigated with XTMR tool (or manually) • uClinux (Let the penguins fly!) • Host to uClinux operating system in a pseudo-MP structure • Provides easy path to high level development for instrument applications (C, sockets, file systems, etc) • Development environment similar (if not identical) to typical Linux desktop 125/MAPLD'05

Development Challenges and Issues • TMR of the reconfigurable logic (especially the Microblaze soft core processor) • Caching architecture across the SLiP interface. • Fabrication with fine pitch CGA components (4VFX60) • Availability of various technologies • Non-volatile memory (FLASH and EEPROM) • Small form factor, high-efficiency DC voltage regulators 125/MAPLD'05

Design Status as of 8/1/2005 • Currently still working architectural formulation, but the base structure is completed. • Reconfigurable nature of the prototype enables architecture trades post hardware development. • Schematics complete and layout proceeding. • Hardware prototypes expected at the end of the fiscal year. 125/MAPLD'05