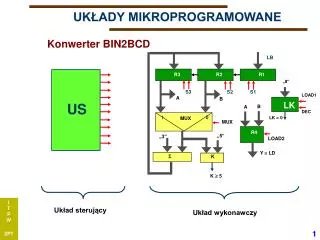

Konwerter BIN2BCD

Konwerter BIN2BCD. R3. R2. R1. 0. 1. MUX. UKŁADY MIKROPROGRAMOWANE. LB. „8”. LOAD1. S3. S2. S1. LK. A. B. DEC. US. LK = 0. MUX. B. A. „5”. „3”. . K. R4. LOAD2. K 5. Y = LD. Układ sterujący. Układ wykonawczy. 1. Dane. wejściowe. Sygnały. sterujące.

Konwerter BIN2BCD

E N D

Presentation Transcript

Konwerter BIN2BCD R3 R2 R1 0 1 MUX UKŁADY MIKROPROGRAMOWANE LB „8” LOAD1 S3 S2 S1 LK A B DEC US LK = 0 MUX B A „5” „3” K R4 LOAD2 K 5 Y = LD Układ sterujący Układ wykonawczy 1

Dane wejściowe Sygnały sterujące Stan części operacyjnej System cyfrowy Układ sterujący (kontroler) Układ wykonawczego Dane wyjściowe

Mikroprogramowany układ sterujący Mikroprogramowany układ sterujący Skoro układ sekwencyjny można opisać siecią działań, to powstaje pytanie, czy nie można takiego układu realizować bezpośrednio – bez przekształcania SD na opis w postaci grafu automatu.

Mikroprogramowany układ sterujący 1. Sekwencyjny układ synchroniczny (Moore’a lub Mealy’ego) 2. Funkcje przejść i wyjść są zapisane w pamięci stałej typu ROM zwanej pamięcią mikroprogramu 3. W każdym takcie pracy układu jest badany (w zasadzie) jeden warunek (sygnał zewnętrzny) spośród zbioru X wszystkich wejść 4. Opis działania za pomocą sieci działań 4

Z1 Z2 x1 xi,...,xk x x2 x3 x1 Z3 Z4 Sieć działań Graf zbudowany z wierzchołków (klatek) i krawędzi Klatki: operacyjne Z Z Z warunkowe selekcyjne

Ai 1 0 Z x 1 0 Za Zb x Aj Ak Mikroinstrukcja - podstawowe segmenty SD MIKROINSTRUKCJA MI (Ai) wygenerowanie mikrorozkazu Z badanie warunku x X określenie adresu A’ następnej wykonywanej mikroinstrukcji Ai Mealy’ego Moore’a Aj Ak Ai : Z = Za, if x then A’ = Aj else A’ = Ak Ai :, if x then Z = Za, A’ = Aj else Z = Zb, A’ = Ak

Stany wewnętrzne Z1 Ai Ai Z2 Aj Z Z x1 1 0 A3 Ai x x2 x3 x1 Z3 Aj Ak 1 0 x Z4 Aj Ak Podział sieci działań… na segmenty odpowiadające mikroinstrukcjom Moore’a A0 A1 A2 A3 A4 A5

A0 A1 Z1 Z2 0 x1 1 A2 0 0 0 x2 x3 x1 Z3 1 1 1 A3 Z4 Sieć działań reprezentuje automat Podział sieci na stany (dla automatu)

RA Takt Sygnały (warunki)zewnętrznei wewnętrzne UA PM MI DMI Dekoder mikroinstrukcji UO Mikroprogramowany układ sterujący Schemat blokowy MUS A

Adres mikroinstrukcji PM Mikroinstrukcja Format mikroinstrukcji Format mikroinstrukcji: MI = <S, B,C, Z> Pola: S - sterujące (kod MI) B - adresowe C - kontrolne Z - operacyjne (mikrorozkaz) S B C Z

Przykład syntezy MUS Mając do dyspozycji licznik o mikrooperacjach LOAD, COUNT ze sterowaniem odpowiednio: 1 (dla LOAD), 0 (dla COUNT), pamięć ROM oraz ewentualnie inne bloki funkcjonalne i bramki, zaprojektować mikroprogramowany układ sterujący o następującej liście mikroinstrukcji I1 : Z, if xc then A’ = Ai else A’ = Ai+1, I2 : Z, if xc then A’ = Ai+2 else A’ = Ai+1, I3 : Z, A’ = Aj. W rozwiązaniu należy podać: – fragmenty sieci działań (schematy) odpowiadające wszystkim mikroinstrukcjom, – schemat blokowy układu sterującego, – tablicę prawdy dekodera mikroinstrukcji oraz minimalne wyrażenia boolowskie opisujące jego wyjścia.

Ai Ai Ai Ai Z Z 1 Z 1 x x Ai+2 0 0 Aj Ai+1 Ai+1 Przykład c.d. - mikroinstrukcje I1 : Z, if xc then A’ = Ai else A’ = Ai+1 (oczekiwanie na spełnienie warunku) I2 : Z, if xc then A’ = Ai+2 else A’ = Ai+1 (skok warunkowy o 2)) I3 : Z, A’ = Aj C, Z C, Z B, Z Formaty mikroinstrukcji

MA +2 Q1 Q0 00 01 11 Formaty mikroinstrukcji LICZNIK L C, Z A C, Z PM B, Z X L s1 s0 DMI Q1 Q0 s1s0 xc Przykład syntezy US - schemat blokowy Adresy: A, A+1, A+2, B B Pola C i B są polami zgodnymi ponieważ nie występują jednocześnie w żadnej mikroinstrukcji. Można je umieścić w jednym segmencie PM B C Z

A+2 MI3 B A MA MI2 MI1 Ai +2 L s1 s0 Q1 Q0 DMI Z Q1 Q0 00 01 11 xc Ai Ai Ai Aj Z Z 1 1 x LICZNIK L x Ai+2 A 0 0 Ai+1 Ai+1 Przykład c.d. – dekoder mikroinstrukcji Count 0 Load 1 L = s1 + xc Q1 = s0xc

Przykład (str. 139 SUL) Zaprojektować układ sterujący o następującej liście mikroinstrukcji: a) Ai : Z, A' = Ai+1 b) Ai : Z, A' = Aj. c) Ai: Z, if xc then A' = Ai+1 else A' = Ai, Ponadto układ ma umożliwiać obsługę mikropodprogramu.

Rejestr Śladu q xc Mikroinstrukcje do obsługi (mikro)podprogramu Warunkowe wejście do podprogramu Ai : if xc then A' = Aj, RS:= Ai+1 else A' = Ai+1 A i adres Ai+1 powrotu z podprogramu zapamiętany w rejestrze śladu RS 1 A RS := A i+1 j Ai+1 0 A k Warunkowe wyjście z podprogramu 1 xc A :=RS A i+1 0 A k+1 Ai : if xc then A' = RS else A' = Ai+1

Przykład c.d. Zaprojektować układ sterujący o następującej liście mikroinstrukcji: a) Ai : Z, A' = Ai+1 b) Ai : Z, A' = Aj. c) Ai: Z, if xc then A' = Ai+1 else A' = Ai, Ponadto układ ma umożliwiać obsługę mikropodprogramu. d) Ai : if xc then A' = Aj, RS:= Ai+1 else A' = Ai+1 e) Ai : if xc then A' = RS else A' = Ai+1 17

Przykład cd. Adresy: Ai+1 Aj Ai RS

Przykład cd. realizacja z rejestrem adresowym Adresy: Ai+1 Aj Ai RS

Przykład cd. realizacja z rejestrem adresowym A Adresy: Ai+1 Aj Ai RS +1 RS q I I I I 0 3 1 2 Q MUXA RA PM S B v Q q v X DMI Z C MUXW x S c x c 20

Przykład cd. • Przejście bezwarunkowe, Z • Skok bezwarunkowy, Z • Przejście warunkowe, Z • Warunkowe wejście do podprogramu • Warunkowe wyjście z podprogramu

Przykład cd. z licznikiem adresowym Adresy: Ai+1 count Ai hold Aj load RS load