Overview of RCC Control Registers and SYSTICK Timer Functionality

This section covers the control provided by RCC registers, including RCC and RCC2, for system clock management. It describes how these registers allow for configuring system clock dividers, enabling or disabling peripheral clocks, and managing power states through deep sleep mode settings. Additionally, the SYSTICK timer's operation and its role in generating exceptions for task management in real-time operating systems are explained. Key functionalities include clock division for ADC operations and the ability to clear COUNTFLAG for effective timer management.

Overview of RCC Control Registers and SYSTICK Timer Functionality

E N D

Presentation Transcript

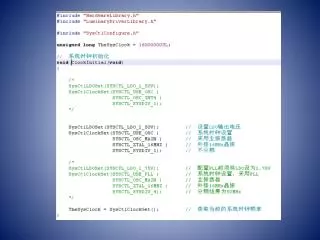

a. Control provided by RCC register bit/field. b. Control provided by RCC register bit/field or RCC2 register bit/field, if overridden with RCC2 register bit USERCC2. c. Control provided by RCC2 register bit/field. d. Also may be controlled by DSLPCLKCFG when in deep sleep mode. e. Control provided by RCC register SYSDIV field, RCC2 register SYSDIV2 field if overridden with USERCC2 bit, or [SYSDIV2,SYSDIV2LSB] if both USERCC2 and DIV400 bits are set. • Figure 5-5 shows the logic for the main clock tree. The peripheral blocks are driven by the system • clock signal and can be individually enabled/disabled. When the PLL is enabled, the ADC clock • signal is automatically divided down to 16 MHz from the PLL output for proper ADC operation. The • PWM clock signal is a synchronous divide of the system clock to provide the PWM circuit with more • range (set with PWMDIV in RCC).

When the SYSTICK timer changes from 1 to 0, it will set the COUNTFLAG bit in the SYSTICK Control and Status register. The COUNTFLAG can be cleared by one of the following: • Read of the SYSTICK Control and Status register by the processor • Clear of the SYSTICK counter value by writing any value to the SYSTICK Current Value register

The SYSTICK counter can be used to generate SYSTICK exceptions at regular intervals. This is often necessary for the OS, for task and resources management. To enable SYSTICK exception generation, the TICKINT bit should be set.