Maintaining Data Integrity in EEPROM’s

Maintaining Data Integrity in EEPROM’s. Ed Patnaude Maxwell Technologies San Diego, Ca. Contents. EEPROM Technology Sources of Data Corruption Maintaining Data Integrity Summary. EEPROM Technology. Most EEPROM’s utilize some variation of the “Floating Gate Technology”.

Maintaining Data Integrity in EEPROM’s

E N D

Presentation Transcript

Maintaining Data Integrity in EEPROM’s Ed Patnaude Maxwell Technologies San Diego, Ca

Contents • EEPROM Technology • Sources of Data Corruption • Maintaining Data Integrity • Summary

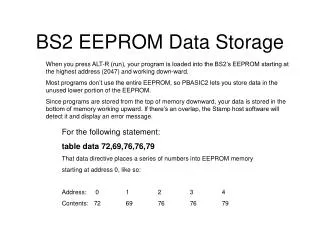

EEPROM Technology Most EEPROM’s utilize some variation of the “Floating Gate Technology” A positively charged gate is read as a logic 0.

Sources of Data Corruption • Software Errors • Insufficient Hardware Protection • Programming Issues

Sources of Data Corruption • Software Errors • Inadvertent Writes • Improper Timing / Buss Contention • Programming Across Page Boundaries

Sources of Data Corruption • Insufficient Hardware Protection • Uncontrolled Power On/Off • Uncontrolled Inputs • Excessive Power Supply Noise • Data Buss Contention • No Hardware Write Protection Implemented

Sources of Data Corruption • Programming Issues • Setting Write Protect, or Reset, active during a write cycle will halt programming resulting in corrupt data. • Insufficient supply voltage, during a program cycle, can result in incorrect data being stored. • Exceeding the manufactures write cycle endurance specification can cause permanent damage to the memory cells leaving them un-programmable.

Maintaining Data Integrity • Hardware Protection • Software Protection • Proper Power Cycling • Error Detection and Correction (EDAC) • Power Supply Supervisory Circuitry • Contingency Plan

Maintaining Data Integrity • Hardware Protection Most EEPROM’s have a RESET or Write Protect input, when set active, all erase/writes operations are blocked.

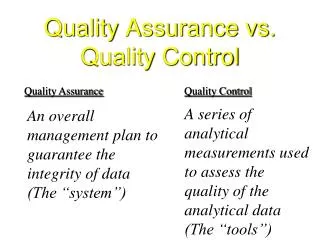

Maintaining Data Integrity • Software Data Protection (SDP) • SDP locks the memory preventing unintentional erase/writes from occurring. • Normally implemented using the JEDEC Standard Algorithm • SDP will only protect the memory contents when the supply voltage is within the normal operating range.

Maintaining Data Integrity • Proper Power Cycling • Allow Vcc to reach proper operating level before initiating any Reads or Writes to the EEPROM. • Enable the EEPROM Hardware Write Protection, or Reset, prior to power down. • Do not remove power while a write cycle is in process.

Maintaining Data Integrity • Error Detection and Protection • Parity Bits • Checksum • Cyclic Redundancy Code • Error Correction Codes • Hamming Code • Reed-Solomon

Maintaining Data Integrity • Power Supervisory Circuitry Monitor Supply Voltages and provide a RESET signal when the voltage drops below a pre-described level

Maintaining Data Integrity • Have a Contingency Plan • Always verify data after a program cycle to assure an error has not occurred and re-program if necessary. • Data retention time can be increased by periodically rewriting the data to the EEPROM. • Have the ability to relocate bad data bytes. • Use Redundancy if at all possible.

Summary A robust hardware and software design, along with a contingency plan should corruption occur, can greatly minimize the risk of system failure due to data corruption in a EEPROM.