Enhancing H.264 Video Decoding for Real-Time HDTV Applications

This document discusses the advancements in the H.264 video coding standard, showcasing its superior compression performance compared to previous standards like H.263 and MPEG4. With bitrate savings of 50%-70% over MPEG-2 and 25%-45% over MPEG-4, the focus is on developing an H.264 BP/MP video decoder optimized for real-time HD1080 applications. Key design goals include low gate count and reduced internal SRAM requirements. Techniques employed for optimization and complexity reduction are outlined, alongside future directions for supporting H.264 High Profile decoding.

Enhancing H.264 Video Decoding for Real-Time HDTV Applications

E N D

Presentation Transcript

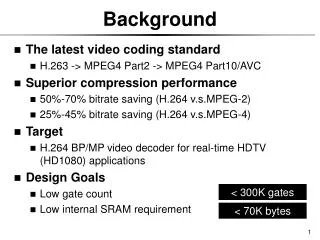

Background • The latest video coding standard • H.263 -> MPEG4 Part2 -> MPEG4 Part10/AVC • Superior compression performance • 50%-70% bitrate saving (H.264 v.s.MPEG-2) • 25%-45% bitrate saving (H.264 v.s.MPEG-4) • Target • H.264 BP/MP video decoder for real-time HDTV (HD1080) applications • Design Goals • Low gate count • Low internal SRAM requirement < 300K gates < 70K bytes

Techniques • Reducing design complexity • C Level algorithm optimization • Hybrid block level pipeline control • 4x4/16x16 block level • Integrating Intra and inter functions • Share the hardware cost • High performance CABAC Decoder • Look ahead scheme with cache register • Reducing memory bandwidth • Hybrid block level Motion Compensation • Share the data and reduce memory access times • Reducing internal SRAM • Prediction Data Store Buffer (PDSB) • Collect the data not used immediately and write them to external memory Reducing 40~60% complexity Reducing 48% of memory BW Reducing 98% of internal memory

Summary • Future direction • Supporting H.264 High Profile (HP) video decoding • Acknowledgements • National Science Council (NSC) • Chip Implementation Center (CIC) Taiwan • Faraday Inc. of Taiwan • FPGA prototyping • Chip implementation Faraday FIE-8100 (Xilinx V2-4000)