Lecture 11 Input Output Systems

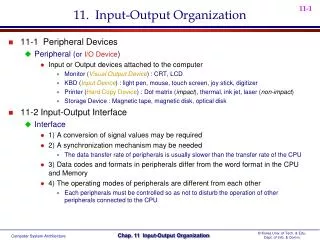

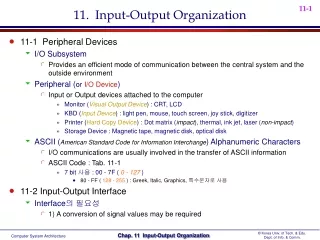

Lecture 11 Input Output Systems. Lecture 11: Input/Output System. In this lecture, we will study Differences between I/O devices and memory Basic I/O and I/O system with I/O controller Bus Protocol Bus arbitration I/O Interface I/O Controller DMA, Channel I/O System Memory mapped I/O

Lecture 11 Input Output Systems

E N D

Presentation Transcript

Lecture 11Input Output Systems Input Output Systems

Lecture 11:Input/Output System In this lecture, we will study • Differences between I/O devices and memory • Basic I/O and I/O system with I/O controller • Bus • Protocol • Bus arbitration • I/O Interface • I/O Controller • DMA, Channel • I/O System • Memory mapped I/O • CPU controlled I/O • DMA controlled I/O • Channel controlled I/O • I/O Processor Input Output Systems

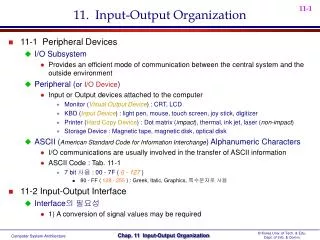

I/O Device and Memory • Input: Memory <= Input Device • Output: Output Device => Memory • Difference between I/O device and memory • Operating Speed • In general, speed of I/O devices is slow than memory • Unit of information • Memory: Word • I/O Device: Byte • Autonomy • Memory is synchronized to CPU clock • I/O devices usually operate asynchronously since they are inherently slow and distance apart from memory(sending CPU clock is expensive) • Error rate • Error rate of I/O Device is much higher than memory Input Output Systems

Input Output Control • I/O device controller • Controls the functions of I/O device • Sometimes it is integrated into the I/O device • e.g. Disk Controller • Moves head to the desired location on the disk surface • Activates the head to read/write access • Sometimes one controller controls many disk drives • I/O controller • Controls the data moves during I/O • Notify an I/O device to initiate the operation and notify the completion of I/O operation to CPU • Establish a connection between memory and an I/O device for data move • Checking the status of I/O operation • Access memory • e.g. CPU, DMA controller, Channel controller, I/O processor, Front end processor Input Output Systems

Memory I/0 Device I/0 Device I/0 Device I/0 Device Memory Bus I/O Dev Controller I/O Dev Controller I/O Dev Controller . . . CPU Interface Interface Interface I/O Bus I/O Controller Basic I/O System Function of I/O Control is included in CPU Input Output Systems

I/O Dev I/O Dev I/O Dev I/O Dev I/O Dev Controller I/O Dev Controller I/O Dev Controller Memory Interface Interface Interface I/O Controller Memory Bus I/O Bus I/O Controller I/O Bus Interface Interface Interface I/O Dev Controller I/O Dev Controller I/O Dev Controller CPU I/O Dev I/O Dev I/O Dev I/O Dev I/O System with I/O Controller Input Output Systems

... Device Device Device Device Bus Bus • Device • Master Device • Acquires the right to use the bus • Performs control operation for actual data transmission • Slave Device • Perform data transmit operation required by the master device • In an instance when a data transmission takes place, one device is the master, and another is the slave. But the roles of device may change. • Some device can be a master in one instance and a slave in other instance Input Output Systems

Master Slave Control Bus Address Bus Data Bus Bus Components • Data Bus • Address Bus • Control Bus • Master sends Control signals and receives status signals In an economical system, One bus can be multiplexed to send Data and Address Input Output Systems

CPU I/O Dev CPU I/O Dev Memory-I/O Common Bus Memory Bus ... I/O Dev Memory I/O Dev I/O Dev I/O Dev Memory I/O Bus Input Output Bus Memory-I/O Common Bus Independent I/O Bus Input Output Systems

Protocol Protocol Communication between devices with widely different characteristics require a communication rule called Protocol • Synchronous Protocol • Asynchronous protocol Input Output Systems

Start Reading Read Complete Clock Pulse Address Data R/W WAIT Synchronous Protocol Synchronous Protocol • Master and Slave devices operate in a synchronized fashion • Information(bit, character, block) is synchronized with the clock pulse • Two different methods • Master sends the clock pulse to the slave with the information • Suitable for short distance • Master and Slave both have the synchronized clock pulse generators which are periodically synchronized • Suitable for long distance communications Input Output Systems

0 1 0 1 1 1 0 0 1 1 1 ... No transmission More than 1 Stop Bits Data Bits Start Bit Asynchronous Protocol:Serial Transmission Asynchronous Serial Transmission Protocol • Master and Slave devices must know • Number of bits in a unit of information(byte) • Transmission rate: bit/sec(Baud rate) Input Output Systems

Request Acknowledge Address Address Next Address Data Data Next Data R/W Next R/W W Req Ack Asynchronous Protocol:Parallel Transmission - Handshaking Protocol Asynchronous Parallel WriteTransmission 1 2 3 4 5 Input Output Systems

Address Address Next Address Data Data Next Data R/W Next R/W R Req Ack Asynchronous Protocol:Parallel Transmission - Handshaking Protocol Asynchronous ParallelRead Transmission 1 4 2 3 5 Input Output Systems

Bus Arbiter Bus Arbitration • In one instance, allow only one master to use the bus • Provides the fairness of the bus use amongst the devices • e.g. priority • 3 bus signals • Bus Request(BR): bus master sends BR to get the right to use the bus • Bus Grant(BG): bus arbiter sends BG to requesting bus master as an authorization of the right to use the bus • A requestor amongst other requestors based on the established fairness rule(e.g., priority) • Bus Busy(BB): the requestor who has the right to use the bus sends BB to notify that bus is in use • 3 different bus arbiter structures • Centralized Parallel Arbitration • Serial Arbitration or Daisy Chain arbitration • Polling Arbitration Input Output Systems

Bus Arbiter (Arbitration Algorithm) BR BB BG BR BB BG BR BB BG . . . Device 0 Device 1 Device n-1 Data Bus Centralized Parallel Arbitration Input Output Systems

Device 0 BGi BGo Device 0 BGi BGo Device 1 BGi BGo Device n BGi BGo BG Bus Arbiter BR BB Data Bus Daisy Chain Arbitration Bus Priority(Arbitration Algorithm) ... • Low priority device may have a danger of starvation • Serial with daisy chain: when there is a failure in the device in the middle of the chain, or broken connection between BGi and BGo, the devices beyond the failing device cannot use the bus Input Output Systems

Device 0 Device 1 . . . Device n Bus Arbiter BR BB Polling Count Data Bus Polling Arbitration Polling Count Order is the Priority order When a bus requesting device gets its device number through polling count, it send BB to arbiter and use the bus. Bus granting time may be too long. Input Output Systems

Input Output Interface Function of the I/O Interface • Recognizing address(device address or device code sent by I/O instruction) • Resolving the characteristic differences between I/O devices and Memory(CPU, I/O Controller) • Speed • Unit of information • Autonomy • Highly functional I/O controllers • DMA, Channel, IOP, FEP • Error rate Input Output Systems

Address Bus DEV SEL DEV SEL 1 0 Device 101101 Interface Device 111111 Interface I/O Interface:Recognizing Device Code • Since there are many I/O devices, a unique device code is assigned to each device. It is received by the interface via address bus. • In each interface, there is a device code decoder 1 0 1 1 0 1 Input Output Systems

Input Data Buffer Input Device Flag Output Data Buffer Output Device Flag I/O Interface:Resolving Speed Difference • Data Buffer and its associated flag • Receiving data from a slower device - Input • Faster device cannot take away data in its own speed, it must wait until data is ready to be taken away • When can it take away? • When the slower device puts the data in the Data Buffer, it sets the Flag. • Data can be taken away from the data buffer when the Flag is set and reset after the data is taken away for the next data input • Sending data to a slower device - Output • Faster device cannot send data in its own speed, it must wait until data is taken by the slower device • Flag is set by the output device after the data in the Data Buffer is output so that the next data to be output can be stored in the Data Buffer • New data can be stored in the Data Buffer only when the Flagis set Input Output Systems

Input to Memory(or CPU) in parallel Input Dev Clock Output Dev Bit Counter Output from Memory(or CPU) Set when 7 Flag I/O Interface:Resolving Information Unit Difference • Bit <=> Byte • Data Buffer • Input Data Buffer • Serial-in Parallel-out • Output Data Buffer • Parallel-in Serial-out Input Output Systems

I/O Interface:Resolving High Error Rate • Parity bit • Even parity(even number of 1’s in data bits + parity bit) 1 0 1 1 1 0 1 1 0 0 1 1 0 1 1 0 • Odd parity(odd number of 1’s in data bits + parity bit) 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 1 • Echo Back • Retry and Timeout • EDC/ECC Input Output Systems

b0b1b2b3b4b5b6 Odd Parity Error Odd Parity Even Parity Error Even Parity Parity bit generator Parity checker Parity Generator/Checker b7 Input Output Systems

Input Output Controller • Functions of I/O Controller • Establishing a connection between I/O Controller and Memory • Storing Memory Address, Direction of data transmission, and Data for memory access • Memory access • Establishing connection between I/O Interface and I/O Controller • Data exchange with I/O device • Notify CPU of completion of I/O operation Input Output Systems

MCR MCG INT DMAR DMAG CPU DMAC R/W ADR DATA . . . data Memory Bus I/O Dev Control Bus Addr Bus Data Bus I/O Bus Memory DMAC as an I/O Controller A DMA input/output transfers a block, a contiguous words, of data(block) CPU initialize DMAC I/O Device Address Function(R/W) Memory Starting Address Number of words I/O Dev to M connection for Cycle Steal by I/O Dev sends DMAR to DMAC DMAC sends MCR to CPU CPU sends MCG to DMAC DMAC send DMAG to I/O Dev DMAC send Addr and Func to M MCR: Memory Cycle Request MCG: Memory Cycle Grant DMAR: DMA Request DMAG: DMA Grant Input Output Systems

DMAR DMAR CPU FET EXE FET EXE FET EXE FET EXE FET . . . M Cycle Interrupt FET EXE FET EXE FET … Interrupt Routine DMAC DMAC DMAC:Cycle Steal • CPU is continuously accessing memory, i.e., using memory cycles during program execution • When a MCR is received, CPU gives the next memory cycle to DMAC so that the requesting I/O Device can use the memory cycle without significant delay that may cause lost data Input Output Systems

I/O Data Bus(8) Interface 8 Input Clock Output SL 8 Data Buffer(32) Memory SR 8 Byte Counter I/O Data(32) =3 Reset Memory Bus Data Buffer Logic F LDB/RDB Control Logic R/W MCR MCG Memory Data Bus(32) CPU Memory Control Bus DMAC:Data Buffer Logic LDB/RDB LDB for output RDB for input Resets Byte Counter Data Buffer Buffer Full when 4B Byte Counter = 3 SL for input from I/O bus SR for output to I/O bus Input Output Systems

Memory Address Buffer Address Buffer Logic +1 =0 Word Counter Word Counter Logic -1 LDB/RDB Control Logic INT MCG CPU DMAC:Address Buffer and Byte Counter Logic Receiving MCG form CPU, either RDB to move Data Buffer to M, or LDB to move M to Data Buffer When a word in the block is done for input/output, Increment the address Decrement the word counter When WC = 0 Implies Completion of I/O Request Interrupt CPU Input Output Systems

Fixed Channel Variable Channel Channel Channel CPU CPU I/O I/O I/O Channel Channel I/O Memory I/O I/O DC Memory Channel I/O I/O I/O Channel Controller A channel Input/Output command transfers multiple blocks of data Input Output Systems

Sub-channel I/O Sub-channel I/O Multiplexer Channel Sub-channel I/O Selector and Multiplexer Channel • Selector Channel • A channel dedicated to an I/O device usually for a high speed device • Multiplexer Channel • A channel is time shared by several sub-channels, where a sub-channel serves for a slow I/O device. Thus a multiplexer channel serves several slow devices in the time multiplexed fashion Input Output Systems

Address Space Memory Space 0 1 9 10 I/O Device 0 11 I/O Device 1 12 I/O Device 2 13 I/O Device 3 99 I/O Device 89 100 n-1 I/O Dev 0 I/O Dev 1 I/O Dev 2 . . . ... I/O Dev 89 Memory Mapped I/O Input/Output Instruction No particular I/O instruction Use Load/Store instructions When 9 <X<100 Load R, X for input Store R, X for output Input Output Systems

n [1] If B=1, Repeat [1]; [2] B 1; [3] If D=0, Repeat [3]; [4] R Input Data Buffer, D 0; [5] If there is more input data goto [3]; [6] B 0, end; Loop1: SBZ X /Skip if B=0 JMP Loop1 START X /B 1 Loop2: SDO X/Skip if D=1 JMP Loop2 IN R, X (M R) (n n-1) (if n>0, JMP Loop2) STOP X /B 0 B=0? y B 1 n D=1? y R Buf, D 0 n End? y Wasting a lot of cycles here,depending on the speed of input device B 0 CPU Controlled I/O:Programmed I/O - Input Most elementary I/O • using B(busy) and D(done) flags Input Output Systems

n [1] If B=1, Repeat [1]; [2] B 1; [3] If D=0, Repeat [3]; [4] Output Data Buffer R, D 0; [5] If there is more input data goto [3]; [6] B 0, end; Loop1: SBZ X /Skip if B=0 JMP Loop1 START X /B 1 Loop2: SDO X/Skip if D=1 JMP Loop2 OUT R, X (R M) (n n-1) (if n>0, JMP Loop2) STOP X /B 0 B=0? y B 1 n D=1? y Buf R, D 0 n End? y Wasting a lot of cycles here,depending on the speed of input device B 0 CPU Controlled I/O:Programmed I/O - Output Most elementary I/O • using B(busy) and D(done) flags Input Output Systems

CPU Controlled I/O:Programmed I/O • Inefficient because CPU wastes a lot of cycles simply waiting for the slow I/O device to respond • Example Speed of CPU = 100 MIPS: Assume that identical instruction execution time Input 1,000 characters from a keyboard, 1 character input time is 1 sec. How many times SDO instruction in Loop2 will be executed per character input ? 100 MIPS implies that execution time of an instruction is 10-8 sec. To simplify the problem, neglect the first three instructions and the last instruction since they are executed only once at the beginning and at the very last. Let X be the number of executions of SDO instruction in Loop2. Number of instruction executions for one character input becomes; X + (X-1) + 4 Thus, (2X + 3) x 10-8 sec = 1 sec Therefore, X = 5 x 107 , i.e., it will be executed 50 million times Input Output Systems

Loop1: SBZ X JMP Loop1 START X Loop2: SDO X JMP Loop2 IN R, X (M R) (n n-1) (if n>0, JMP Loop2) STOP X Waste of CPU cycles in programmed I/O By allowing Device X to interrupt CPU when data buffer is ready, this much CPU cycles can be utilized for the productive work. Loop1: SBZ X JMP Loop1 START X Loop3: ION X ( Execute other tasks ………….. ) IN R, X (M R) (n n-1) (if n>0, JMP Loop3) STOP X Interrupt from X Done in the interrupt processing routine CPU Controlled I/O:Interrupt Processed I/O Interrupt processed I/O allows to utilize the slow I/O device’s response time for the productive work, if there is any Input Output Systems

DMAC Controlled I/O • CPU must send DMAC with • Direction of data transfer, i.e., Function(R or W) • Starting address of the block • Word count • (Address of DMAC), I/O device address • (Data block address in I/O device) • Instruction • Output instruction if programmed I/O system is used • ST instruction if memory mapped I/O system is used Input Output Systems

CCW0 CCW1 CCW2 CCWn . . . CAW Channel I/O • Channel Program stored in memory • Channel program consists of a linked list of Channel Command Words(CCW) • Instruction • STARTCn, Dn • CAW • CCW • Information provided to DMAC about data block and direction of transfer Input Output Systems

Off-line Main Computer Dedicated I/O Computer Mag Tape Mag Tape Printer CPU Memory CPU Memory Graphics Dev On-line Computer Disk Disk Input Output Processor Input/Output Processor • Handling of Data to be input/output • Editing, Debugging, Validating, … • 2 kinds of I/O Processors(computers) • Off-line I/O computers • On-line I/O computers Input Output Systems

I/O Computer Main Computer Printer CPU CPU Graphics Dev Memory Memory Computer Disk I/O Computer Main Computer Printer CPU CPU Graphics Dev Memory Memory Computer On-line I/O Computers Input Output Systems