VHDL Lecture 1

VHDL Lecture 1. Megan Peck EECS 443 Spring 08. Modeling Digital Systems. We use VHDL to implement system models For this class you will use simulation to test the correctness of models The design process will be: Develop a design to meet the problem specification

VHDL Lecture 1

E N D

Presentation Transcript

VHDL Lecture 1 Megan Peck EECS 443 Spring 08

Modeling Digital Systems • We use VHDL to implement system models • For this class you will use simulation to test the correctness of models • The design process will be: • Develop a design to meet the problem specification • Implement the design using VHDL • Implement a simulation testbench to test the correctness of your design and implementation

Entity Declaration • Say we want to design a 4-bit register, with enable and clock. We could do this 2 different ways: 1 2 4 4 d0 q0 d q d1 q1 d2 q2 d3 q3 en en clk clk

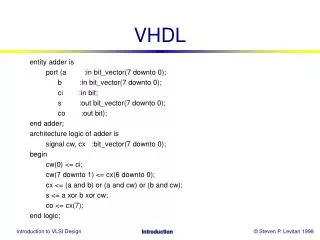

Design 1: entity reg4 is port(d0,d1,d2,d3,en,clk: in std_logic; q0,q1,q2,q3 : out std_logic); end entity reg4; • Design 2: entity reg4 is port(d : in std_logic_vector(3 downto 0); en, clk : in std_logic; q : out std_logic_vector(3 downto 0)); end entity reg4;

Architectures • The architecture contains the implementation for the entity • There can be multiple architectures per entity • Behavioral Architecture--Description of the algorithm • They are made up of processes, which contain sequential statements • Sequential statements include signal assignments and wait statements

Behavioral Architecture for Design 1 architecture beh of reg4 is begin update: process (d0,d1,d2,d3,en,clk) is begin -- if register is enabled, and rising-edge clock, update outputs if en=‘1’ and clk=‘1’ and clk’event then q0<=d0; q1<=d1; q2<=d2; q3<=d3; end if; end process update; end architecture beh;

Notes on Behavioral Architectures • Signals – wires; concurrent assignment q0<=d0; -- these happen at the same time q1<=d1; -- • Variables – State; sequential assignment var1:=d0; -- these happen sequential var2:=var1 or ‘1’; -- there is state (memory) associated with -- the variables • Internal signals declared at top of architecture • Internal variables declared at top of process

d q clk d q clk d q clk d q clk Structural Architectures • Think of this as building an architecture using existing building-blocks, and connecting the signals. We could make our 4-bit register out of 4 flip-flops: • Can you think of ways using gates to implement enable? What if we wanted to add a reset? do qo d1 q1 d2 q2 d3 q3 clk

Structural Architecture implementation • Say we have already implemented the entity d_latch with architecture beh (with input bits d,clk; output bit q), • We also have the entitiy and2 (an and gate), with architecture beh. • We will and the clock with enable to send to the clk input of each gate (note: it is not an ideal design to send your clock through logic gates).

architecture struct of reg4 is signal internal_clk : std_logic; -- Note: no direction(in/out) for internal signals begin bit0: entity work.d_latch(beh) port map(d0,int_clk,q0); bit1: entity work.d_latch(beh)) port map(d1,int_clk,q1) bit1: entity work.d_latch(beh)) port map(d1,int_clk,q1) bit1: entity work.d_latch(beh)) port map(d1,int_clk,q1) clock: entity work.and2 port map(clk,en,int_clk); end struct;

Notes on Structural Architectures • There should be NO processes • The port maps tell you what signals in your structural architecture gets mapped to the signals in the entities. You may be mapping port signals or internal signals. Make sure you order them correctly. Let’s look at the latch entity compared to the first instantiations of a latch in the architecture: d_latch entity declaration: entity d_latch is port (d,clk : in std_logic; q : out std_logic); end entity d_latch; d_latch instantiation bit0: entity work.d_latch(beh) port map(d0,int_clk,q0); So, here we are saying d0 goes to the input d, int_clk goes to the input clk, and q0 goes to the ouput q.

Mixed Behavioral and Structural • A mixed architecture will have instantiated components and behavioral processes.

Test Benches • Test benches help determine the correctness of a design. • The steps of a testbench are: • Instantiate the component(s) to be tested • Drive the components’ signals • Wait • Look at the waveforms generated by the testbench to determine if the design is correct (note: some problems might be with the testbench, and not the original design)

Example Testbench entity tb is -- Note: there are no signal ports end entity tb; architecture test_reg4 of tb is -- all port signals from component under test are now internal signals signal d0,d1,d2,d3,en,clk,q0,q1,q2,q3: std_logic; begin -- instantiate component(s) under test -- (dut stands for device under test - name doesn’t matter) dut: entity work.reg4(beh) -- this means pick the beh architecture to test port map(d0,d1,d2,d3,en,clk,q0,q1,q2,q3); drive: process is begin d0<='1'; d1<='1'; d2<='1'; d3<='1'; wait for 20 ns; -- nothing changes, because en!=1 en <= '1'; d0<='0'; d1<='1'; d2<='0'; d3<='1'; wait for 20 ns; -- output should change now d0<='1'; d1<='0'; d2<='1'; d3<='0'; wait for 20 ns; wait; -- This wait is very important. This is what will stop your simulation. -- It should be at the end of every testbench process end process drive; clock: process is begin for i in 0 to 10 loop clk <= '0'; wait for 5 ns; clk <= '1'; wait for 5 ns; end loop; wait; end process clock; end test_reg4;