第二章 基本逻辑运算及集成逻辑门

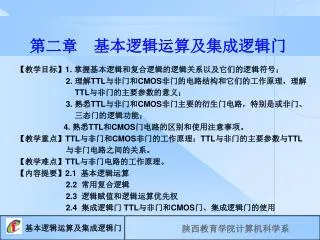

第二章 基本逻辑运算及集成逻辑门. 【 教学目标 】1. 掌握基本逻辑和复合逻辑的逻辑关系以及它们的逻辑符号; 2. 理解 TTL 与非门和 CMOS 非门的电路结构和它们的工作原理,理解 TTL 与非门的主要参数的意义; 3. 熟悉 TTL 与非门和 CMOS 非门主要的衍生门电路,特别是或非门、 三态门的逻辑功能; 4. 熟悉 TTL 和 CMOS 门电路的区别和使用注意事项。 【 教学重点 】TTL 与非门和 CMOS 非门的工作原理; TTL 与非门的主要参数与 TTL 与非门电路之间的关系。

第二章 基本逻辑运算及集成逻辑门

E N D

Presentation Transcript

第二章 基本逻辑运算及集成逻辑门 【教学目标】1. 掌握基本逻辑和复合逻辑的逻辑关系以及它们的逻辑符号; 2. 理解TTL与非门和CMOS非门的电路结构和它们的工作原理,理解 TTL与非门的主要参数的意义; 3. 熟悉TTL与非门和CMOS非门主要的衍生门电路,特别是或非门、 三态门的逻辑功能; 4. 熟悉TTL和CMOS门电路的区别和使用注意事项。 【教学重点】TTL与非门和CMOS非门的工作原理;TTL与非门的主要参数与TTL 与非门电路之间的关系。 【教学难点】TTL与非门电路的工作原理。 【内容提要】2.1 基本逻辑运算 2.2 常用复合逻辑 2.3 逻辑赋值和逻辑运算优先权 2.4 集成逻辑门 TTL与非门和CMOS门、集成逻辑门的使用

2.1 基本逻辑运算 逻辑运算是逻辑思维和逻辑推理的数学描述。 具有“真”与“假”两种可能,并且可以判定其“真”、“假”的陈述语句叫逻辑变量。一般用英文大写字母A、B、 C、 …表示。例如:“开关A闭合着”、“电灯F亮着”、 “开关D开路着”等均为逻辑变量,可分别将其记作A,F,D; “开关B不太灵活”、 “电灯L价格很贵”等均不是逻辑变量。 逻辑变量只有“真”、“假”两种可能,在逻辑数学中,把“真”、 “假”称为逻辑变量的取值,简称逻辑值,也叫逻辑常量。通常用“1”表示“真”,用“0”表示“假”,或者相反。本教材中,若不作特别说明,“1”就代表“真”,“0”就代表“假”。 虽然“1”和“0”叫逻辑值或逻辑常量,但是它们没有“大小”的含义,也无数量的概念。它们只是代表逻辑“真”、“假”的两个形式符号。

一个结论成立与否,取决于与其相关的前提条件是否成立。结论与前提条件之间的因果关系叫逻辑函数。通常记作:一个结论成立与否,取决于与其相关的前提条件是否成立。结论与前提条件之间的因果关系叫逻辑函数。通常记作: F=f(A, B, C, …) 逻辑函数F也是一个逻辑变量,叫做因变量或输出变量。 因此它们也只有“1”和“0”两种取值,相对地把A、 B、 C、…叫做自变量或输入变量。

一、与逻辑(与运算、 逻辑乘) 决定某一结论的所有条件同时成立,结论才成立,这种因果关系叫与逻辑,也叫与运算或叫逻辑乘。 【例】描述图2-1所示电路的功能。 【解】根据左图,描述其功能为:“开关A闭合,并且开关B闭合,则电灯F亮”。状态表见2-1(a) 这三个陈述语句均具有“真”、 “假”两种可能,其对应关系如表2-1(b)所示。 图2-1 与门逻辑电路实例图

若用“1”代表逻辑“真”,用“0” 代表逻辑“假”,则表2-1(b)可改为表2-1(c)的形式。这种表格叫真值表。 所谓真值表,就是将输入变量的所有可能的取值组合对应的输出变量的值一一列出来的表格,是描述逻辑功能的一种重要形式。 表 2-1 与逻辑的真值表

由表2-1可知,上述三个语句之间的因果关系属于与逻辑。 其逻辑表达式(也叫逻辑函数式)为: F=A·B 读作“F等于A乘B”。在不致于混淆的情况下,可以把符号“·”省掉。在有些文献中,也采用∩、∧、&等符号来表示逻辑乘。 由表2-1的真值表可知,逻辑乘的基本运算规则为: 0·0=0 0·1=0 1·0=0 1·1=1 0·A=0 1·A=A A·A=A

实现“与运算”的电路叫与门,其逻辑符号如图2-2所示, 其中图(a)是我国常用的传统符号,图(b)为国外流行符号,图(c)为国家标准符号。 图2-2 与门的逻辑符号

二、 或逻辑(或运算、逻辑加) 决定某一结论的所有条件中, 只要有一个成立, 则结论就成立,这种因果关系叫或逻辑。 【例】描述图2-3所示电路的功能。 【解】根据左图,描述如下:“开关A断开,开关B也断开,则电灯F熄灭”。显然这三个语句都是逻辑变量,分别记作A,B,F。其真值表如表2-2所示。 由表2-2可知,上述三个语句之间的因果关系属于或逻辑。 其逻辑表达式为: F=A+B 读作“F等于A加B”。有些文献也采用∪、∨等符号来表示逻辑加。 图2-3 或逻辑电路实例图

由表2-2的真值表可知,逻辑加的运算规则为: 0+0=0 0+1=1 1+0=1 1+1=1 0+A=A 1+A=1 A+A=A 实现“或运算”的电路叫或门,其逻辑符号如图2-4所示。 表 2-2 或逻辑的真值表

三、非逻辑(非运算, 逻辑反) 若前提条件为“真”,则结论为“假”;若前提条件为“假”,则结论为“真”。即结论是对前提条件的否定, 这种因果关系叫非逻辑。 【例】描述图2-5所示电路的功能。 【解】根据左图,描述如下:“若开关A闭合,则电灯F就亮”。 把以上两个陈述句分别记作A、 F,则其真值表如表2-3所示。 图 2-5 非门逻辑电路实例图

表2-3 非逻辑的真值表 由表2-3的真值表可知,上述两个语句之间的因果关系属于非逻辑,也叫非运算或者叫逻辑反。其逻辑表达式为: 读作“F等于A非”。 通常称A为原变量, 为反变量, 二者共同称为互补变量。 完成“非运算”的电路叫非门或者叫反相器,其逻辑符号如图2-6所示。

图2-6 非门的逻辑符号 (a) 常用符号; (b) 国外流行符号; (c) 国标符号 非运算的运算规则是:

2.2 常用复合逻辑 一、“与非”逻辑 “与非”逻辑是“与”逻辑和“非”逻辑的组合。 先“与”再“非”。 其表达式为: 实现“与非”逻辑运算的电路叫“与非门”,其逻辑符号如图2-7所示。

图 2-7 与非门的逻辑符号 (a) 常用符号; (b) 国外流行符号; (c) 国标符号

二、“或非”逻辑 “或非”逻辑是“或”逻辑和“非”逻辑的组合。 先“或”后“非”。 其表达式为: 实现“或非”逻辑运算的电路叫“或非门”。其逻辑符号如图2-8所示。 图2-8 或非门的逻辑符号 (a) 常用符号; (b) 国外流行符号; (c) 国标符号

三、“与或非”逻辑 “与或非”逻辑是“与”、“或”、“非”三种基本逻辑的组合。 先“与”再“或”最后“非”。 其表达式为: 实现“与或非”逻辑运算的电路叫“与或非门”。其逻辑符号如图2-9所示。 图2-9 与或非门的逻辑符号 (a) 常用符号; (b) 国外流行符号; (c) 国标符号

四、“异或”逻辑及“同或”逻辑 1. 两变量的“异或”及“同或”逻辑 若两个输入变量A、B的取值相异,则输出变量F为1;若A、B的取值相同, 则F为0。这种逻辑关系叫“异或”逻辑,其逻辑表达式为: 读作“F等于A异或B”。 “异或”运算也叫“模2加”运算。

实现“异或”运算的电路叫“异或门”。 其逻辑符号如图2-10 所示。 图 2- 10 异或门的逻辑符号 (a) 常用符号; (b) 国外流行符号; (c) 国标符号 若两个输入变量A、B的取值相同,则输出变量F为1; 若A、B取值相异, 则F为0。这种逻辑关系叫“同或”逻辑,也叫“符合”逻辑。其逻辑表达 式为:

实现“同或”运算的电路叫“同或门”。 其逻辑符号如图2 - 10所示。 图 2 – 10 同或门的逻辑符号 (a) 常用符号; (b) 国外流行符号; (c) 国标符号

两变量的“异或”及“同或”逻辑的真值表如表2 - 4所示。 表 2-4 “异或”及“同或”逻辑真值表

反函数的定义:对于输入变量的所有取值组合,函数F1和F2的取值总是相反,则称F1和F2互为反函数。记作: 由表2 - 4可知,两变量的“异或逻辑”和“同或逻辑”互为反函数。即 由对偶规则(见第三章)可知, AB和A⊙B互为对偶式。

2. 多变量的“异或”及“同或”逻辑 多变量的“异或”或“同或”运算, 要利用两变量的“异或门”或“同或门”来实现。实现电路分别如图2-11和图2-12所示。 图 2 – 11 多变量的“异或”电路

由图2 - 11(a)得: 由图2 - 11(b)得: 由图2 - 12(a)得: 由图2 - 12(b)得:

(1) n个变量的“异或”逻辑的输出值和输入变量取值的对应关系是:输入变量的取值组合中,有奇数个1时,“异或”逻辑的输出值为1;反之,输出值为0。利用此特性,可作为奇偶校验码校验位的产生电路。 “异或”逻辑电路,可以用作奇校验码的接收端的错码检测电路。当它输出“0”时,表示输入代码有错码;当它输出“1”时,表示输入代码基本无错码。 (有可能有偶数位错码,但发生的概率很小。)也可用于偶校验码的错码检测,只是其输出值“1”和“0”的含义与检测奇校验码时相反。

(2) 偶数个变量的“同或”,等于这偶数个变量的“异或”之非。如: A⊙B= A⊙B⊙C⊙D= 奇数个变量的“同或”, 等于这奇数个变量的“异或”。如: A⊙B⊙C=

2.3 正 负 逻 辑 2.3.1 正负逻辑 在数字系统中,逻辑值是用逻辑电平表示的。若用逻辑高电平UOH表示逻辑“真”,用逻辑低电平UOL表示逻辑“假”,则称为正逻辑;反之,则称为负逻辑。本教材采用正逻辑。 当规定“真”记作“1”,“假”记作“0”时,正逻辑可描述为: 若UOH代表“1”,UOL代表“0”,则为正逻辑;反之,则为负逻辑。 UOH和UOL统称为逻辑电平,其值因逻辑器件内部结构不同而异(后述)。 UOH和UOL的差值(叫逻辑摆幅)愈大,则“1”和“0”的区别越明显,电路可靠性越高。

2.3.2 逻辑运算的优先级别 逻辑运算的优先级别决定了逻辑运算的先后顺序。 在求解逻辑函数时,应首先进行级别高的逻辑运算。各种逻辑运算的优先级别,由高到低的排序如下: 长非号是指非号下有多个变量的非号。

2.3.3 逻辑运算的完备性 “与”、“或”、“非”是逻辑代数中三种最基本的逻辑运算。 任何逻辑函数都可以用这三种运算的组合来构成。即任何数字系统都可以用这三种逻辑门来实现。因此,称“与”、“或”、 “非”是一个完备集合,简称完备集。但是,它不是最好的完备集,因为用它实现逻辑函数,必须同时使用三种不同的逻辑门,这对数字系统的制造、维修都不方便。由反演律(见逻辑代数一章)可以看出,利用“与”和“非”可以得出“或”;利用“或”和“非”可以得出“与”。因此,“与非”、“或非”、 “与或非”这三种复合运算中的任何一种都能实现“与”、 “或”、“非”的功能,即这三种复合运算各自都是完备集。因此,利用“与非门”、“或非门”、“与或非门”中的任何一种, 都可以实现任何逻辑函数,这给数字系统的制造、维修带来了极大的方便。

2.4 集 成 逻 辑 门 把若干个有源器件和无源器件及其连线,按照一定的功能要求,制做在同一块半导体基片上,这样的产品叫集成电路。若它完成的功能是逻辑功能或数字功能, 则称为逻辑集成电路或数字集成电路。最简单的数字集成电路是集成逻辑门。 集成逻辑门,按照其组成的有源器件的不同可分为两大类: 一类是双极性晶体管逻辑门;另一类是单极性绝缘栅场效应管逻辑门,简称MOS门。

双极性晶体管逻辑门主要有TTL门(晶体管-晶体管逻辑门)、ECL门(射极耦合逻辑门)和I2L门(集成注入逻辑门)等。 单极性MOS门主要有PMOS门(P沟道增强型MOS管构成的逻辑门)、NMOS门(N沟道增强型MOS管构成的逻辑门)和CMOS门(利用PMOS管和NMOS管构成的互补电路构成的门电路,故又叫做互补MOS门

2.4.1 TTL与非门 典型的TTL与非门的电路图如图2 - 13(a)所示。 图 2 – 13 典型的TTL与非门电路 (a) 电路原理图; (b) 多射极晶体管的等效电路

1. 电路结构 多发射极晶体管V1和电阻R1构成输入级。其功能是对输入变量A、B、C实现“与运算”,如图2 - 13(b)所示。 晶体管V2和电阻R2、R3构成中间级。其集电极和发射极各输出一个极性相反的电平,分别用来控制晶体管V4和V5的工作状态。 晶体管V3、V4、V5和电阻R4、R5构成输出级,它们的功能是非运算。 在正常工作时,V4和V5总是一个截止,另一个饱和。

2. 功能分析 (1) 输入端至少有一个为低电平(UIL=0.3V)。当输入端至少有一个接低电平UIL(0.3V)时,接低电平的发射结正向导通,则V1的基极电位UB1=UBE1+UIL=0.7+0.3=1V。为使V1的集电结及V2和V5的发射结同时导通,UB1至少应当等于2.1V(UB1=UBC1+UBE2+UBE5)。现在UB1=1V,所以,V2和V5必然截止。由于V2截止,故IC2≈0,R2中的电流也很小, 因而R2上的电压很小。因此有

该电压使V3和V4的发射结处于良好的正向导通状态,V5处于截止状态,此时输出电压等于高电平(3.6 V)。 UO=UOH=UC2-UBE3-UBE4=5-0.7-0.7=3.6V 此值未计入R2上的压降,所以实际的UOH小于3.6V。 当UO=UOH时,称与非门处于关闭状态。

(2) 输入端全部接高电平(UIH=3.6V)。V1的基极电位UB1最高不会超过2.1V。因为当UB1≥2.1V时,V1的集电结及V2和V5的发射结会同时导通,把UB1钳在UB1=UBC1+UBE2+UBE5=0.7+0.7+0.7=2.1V。所以,当各个输入端都接高电平UIH(3.6V)时,V1的所有发射结均截止。这时+UCC通过R1使V1的集电结及V2和V5的发射结同时导通,从而使V2和V5处于饱和状态。此时V2的集电极电位为: UC2=UCES2+UBE5≈0.3+0.7=1V

UC2加到V3的基极,由于R4的存在,可以使V3导通。所以,V4的基极电位和射极电位分别为: • UB4=UE3≈UC2-UBE3=1-0.7=0.3V • UE4=UCES5≈0.3V • 可见,V4的发射结偏压UBE4=UB4-UE4=0.3-0.3=0V,所以,V4处于截止状态。 • 在V4截止、V5饱和的情况下,输出电压UO为: • UO=UOL=UCES5≈0.3V • UO=UOL时,称与非门处于开门状态。

综上所述,当输入端至少有一端接低电平(0.3V)时, 输出为高电平(3.6V);当输入端全部接高电平(3.6V)时, 输出为低电平(0.3 V)。由此可见,该电路的输出和输入之间满足“与非”逻辑关系

(3) 输入端全部悬空。输入端全部悬空时,V1管的发射结全部截止。+UCC通过R1使V1的集电结及V2和V5的发射结同时导通,使V2和V5处于饱和状态,则UB3=UC2=UCES+UBE5=0.3+0.7=1V。由于R4的作用,V3导通, 故UBE3=0.7 V。此时V2的发射结电压为: UBE4=UB4-UE4=UE3-UCES5=UB3-UBE3-UCES5 ≈1-0.7-0.3=0 V 所以V4处于截止状态。

可见该电路在输入端全部悬空时,V4截止,V5饱和。故其输出电压UO为: UO=UCES5≈0.3V 可见输入端全部悬空和输入端全部接高电平时,该电路的工作状态完全相同。所以,TTL电路的某输入端悬空,可以等效地看作该端接入了逻辑高电平。实际电路中,悬空易引入干扰,故对不用的输入端一般不悬空, 应作相应的处理。

(4) 一个输入端通过电阻RE接地,其它输入端接高电平。 设V1的发射极A通过RE接地,其它输入端均接高电平,如图2 - 14所示。在+UCC的作用下,接RE的发射结必然导通,在RE上形成电压UEA。RE越大,其压降UEA越大。实验测知,只要RE≤0.7 kΩ,其端电压就相当于逻辑低电平。使与非门输出高电平,即与非门处于关门状态。只要RE≥2kΩ,则其端电压UEA达到1.4V,此时V1管的基极电位UB1=UBE1+UEA=0.7+1.4=2.1V,从而使V5导通,V4截止,与非门输出低电平,即与非门处于开门状态。由于V1管的基极电位UB1不可能高于2.1V,因此,不管RE的阻值有多大,其端电压最高为1.4 V。该电压值虽然与高电平(3.6)相差甚远,但其效果相当于在该端接入了高电平。

当与非门的某一输入端通过电阻RE接参考地(其它输入端接高电平)时,为使与非门可靠地工作在关门状态,RE所允许的最大阻值叫该与非门的关门电阻,记作ROFF。为使与非门可靠地工作在开门状态,RE所允许的最小阻值叫该与非门的开门电阻,记作RON。由上述分析可知,典型TTL与非门的ROFF=0.7 kΩ,RON=2kΩ。考虑到不同类型的TTL与非门,其内部结构及元件参数会有所不同,故它们的ROFF及RON也会有所差异。所以,在工程技术中,TTL与非门的ROFF和RON分别取值为0.5 kΩ和2 kΩ。 综合上述,当TTL与非门的某一输入端通过电阻R接地时,若R≤0.5kΩ,则该端相当于输入逻辑低电平;若R≥2 kΩ,则该端相当于输入逻辑高电平。

3. 主要参数 对器件的使用者来说, 正确地理解器件的各项参数是十分重要的。 (1) 输出高电平UOH和输出低电平UOL。与非门至少一个输入端接低电平时的输出电压叫输出高电平,记作UOH。不同型号的TTL与非门,其内部结构有所不同,故其UOH也不一样。 即使同一个与非门,其UOH也随负载的变化表现出不同的数值。 但是只要在2.4~3.6V之间即认为合格。UOH的标准值是3V。 与非门的所有输入端都接高电平时的输出电压叫输出低电平,记作UOL。其值只要在0~0.5V之间即认为合格。UOL的标准值是0.3V。

(2) 开门电平UON和关门电平UOFF。开门电平UON是保证与非门输出标准低电平时,允许输入的高电平的最小值。 只有输入电平大于UON,与非门才进入开门状态,输出低电平。即UON是为使与非门进入开门状态所需要输入的最低电平。一般产品规定UON在1.4~1.8 V之间。 关门电平UOFF是保证与非门输出标准高电平的90%(2.7 V)时,允许输入的低电平的最大值。只有输入电平低于UOFF,与非门才进入关门状态,输出高电平。即UOFF是为使与非门进入关门状态所需要输入的最高电平。一般产品规定UOFF在0.8~1 V之间。

(3) 噪声容限UNH和UNL。当与非门的输入端全接高电平时,其输出应为低电平,但是若输入端窜入负向干扰电压,就会使实际输入电平低于UON,致使输出电压不能保证为低电平。在保证与非门输出低电平的前提条件下, 允许叠加在输入高电平上的最大负向干扰电压叫高电平噪声容限(或叫高电平干扰容限),记作UNH。其值一般为: UNH=UIH-UON=3-1.8=1.2V 式中,UIH=3 V是输入高电平的标准值。

当与非门的输入端接有低电平时,其输出应为高电平。 若输入端窜入正向干扰,以致使输入低电平叠加上该干扰电压后大于UOFF,则输出就不能保证是高电平。 在保证与非门输出高电平的前提下,允许叠加在输入低电平上的最大正向干扰电压叫低电平噪声容限(或叫低电平干扰容限),记作UNL。 其值一般为: UNL=UOFF-UIL=0.8-0.3=0.5V 式中,UIL=0.3V是输入低电平的标准值。

(4) 平均传输延迟时间tpd。平均传输延迟时间是衡量门电路运算速度的重要指标。当输入端接入输入信号后,需要经过一定的时间td,才能在输出端产生对应的输出信号。 td就叫传输延迟时间。 从输入端接入高电平开始,到输出端输出低电平为止,所经历的时间叫导通延迟时间,记作tpHL。测试时,把输入波形的上升边沿的中点,到对应输出波形下降边沿的中点之间的时间间隔作为tpHL的值。如图2 - 15所示。