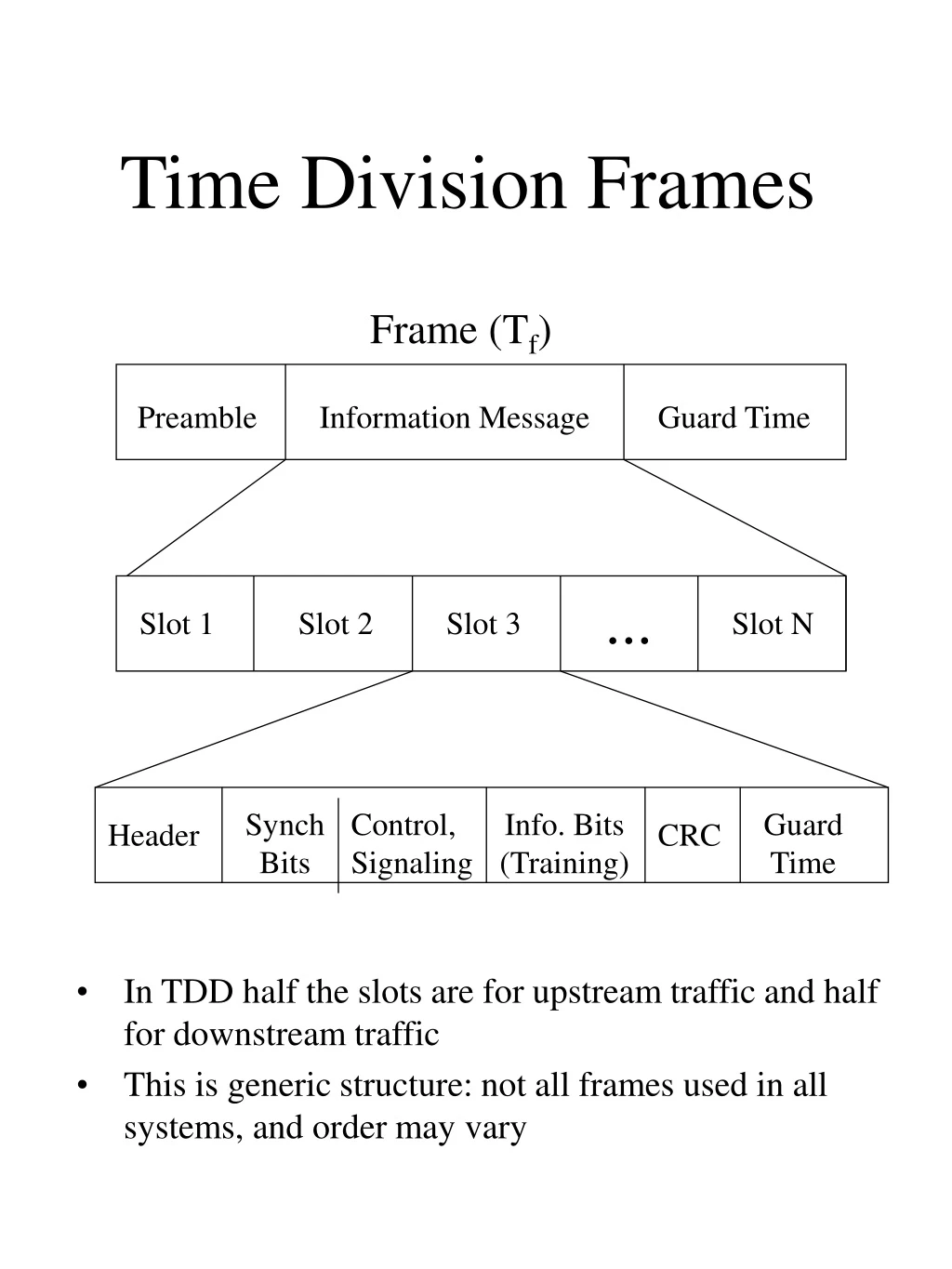

Time Division Frames

E N D

Presentation Transcript

Preamble Information Message Guard Time ... Slot N Slot 1 Slot 2 Slot 3 Synch Bits Control, Signaling Info. Bits (Training) Guard Time Header CRC Time Division Frames Frame (Tf) • In TDD half the slots are for upstream traffic and half for downstream traffic • This is generic structure: not all frames used in all systems, and order may vary

Frame Details • Preamble contains address and sync information used by base and mobile • Guard times allow sync of receivers between different frames • Users are assigned a position in each frame (delay of Tf between bursts) • Superframes (frames of frames) may have additional control frames

Slot Structure • Header:guard (ramp) time for receiver synch. between slots • Synch:Used to establish bit synch (also for equalizer training) • Control:Used for handshaking, control, and supervisory messages • Info. Bits: Coded or uncoded information bits, may include pilot symbols/sequences for channel measurement and equalizer training. • Guard Time: Prevents overlap at base of slots arriving from different terminals.

Requirements • Equalizer requirements: adaptive equalizer must compensate for time-varying ISI. • Minimum N=t/Ts symbols for training. • For t=20msec and Rb=280 Kbps, N=6 minimum (GSM: N=26) • If Tf~Tc, need to retrain every frame (GSM: Tf=4.615 ms, Tc=fD-1=12.5ms for fD=80 Hz, retrains every frame). • Guard time requirements: must compensate for LOS propagation delay (R/c for R the cell radius) and delay spread t due to multipath (reverse link only). • No delay spread: Tg>R/c=3.3 msec for R=1Km. • Do not need guard time for LOS propagation delay if base station synchronizes to received (instead of transmitted) signal. • With delay spread t: Tg>R/c+t, but typically have a smaller guard time.

Tail 3b Data 57b Flag 1b Flag 1b Equal. Train 26b Data 57b Tail 3b Guard 8.25ms GSM Slots • Multiframe has 26 frames (each frame is 4.615ms), with 24 for data and 2 for control. Each call in progress assigned a control channel. • Slot time is 577ms • 26b equalizer training designed to handle delay spread up to 20 msec. (equalizer design not part of spec.) • Guard time less than maximum t. • Flag bits distinguish voice from data • Transmission rate approx. 270 Kb/s

Spread Spectrum MAC • Basic Features • signal spread by a code • synch. between pairs of users • compensation for near-far problem (in MAC channel) • compression and channel coding • Spreading Mechanisms • direct sequence multiplication • frequency hopping Note: spreading is 2nd modulation (after bits encoded into digital waveform, e.g. BPSK), and DS spreading codes are inherently digital.

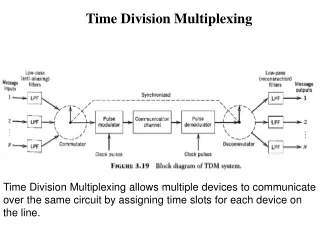

Linear Modulation. (PSK,QAM) d(t) s(t) Linear Demod. X X Channel Sci(t) Sci(t) SS Modulator SS Demodulator Direct Sequence • Chip time Tc is N times the symbol time Ts. • Bandwidth of s(t) is N+1 times that of d(t). • Channel introduces noise, ISI, and multiple access interference.

sci(t) s(t) BPSK Example d(t) Tb Tc=Tb/10

Code Properties • Good code designs have r(t)=d(t) and rij(t)=0 for all t. • Hard to get these properties simultaneously.

Walsh-Hadamard Codes • For N chips/bit, can get N orthogonal codes • Bandwidth expansion factor is roughly N. • Roughly equivalent to TD or FD from a capacity standpoint • Multipath destroys code orthogonality.

Semi-Orthogonal Codes • Maximal length feedback shift register sequences have good properties • In a long sequence, equal # of 1s and 0s. • No DC component • A run of length r chips of the same sign will occur 2-rl times in l chips. • Transitions at chip rate occur often. • The autocorrelation is small except when t is approximately zero • ISI rejection. • The cross correlation between any two sequences is small (roughly rij=G-1/2 , where G=Bss/Bs) • Minimizes MAC interference rejection