第 2 章

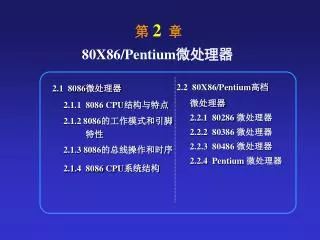

第 2 章. 80X86/Pentium 微处理器. 2.1 8086 微处理器 2.1.1 8086 CPU 结构与特点 2.1.2 8086 的工作模式和引脚 特性 2.1.3 8086 的总线操作和时序 2.1.4 8086 CPU 系统结构. 2.2 80X86/Pentium 高档 微处理器 2.2.1 80286 微处理器 2.2.2 80386 微处理器 2.2.3 80486 微处理器

第 2 章

E N D

Presentation Transcript

第 2章 80X86/Pentium微处理器 2.1 8086微处理器 2.1.1 8086 CPU结构与特点 2.1.2 8086的工作模式和引脚 特性 2.1.3 8086的总线操作和时序 2.1.4 8086 CPU系统结构 2.2 80X86/Pentium高档 微处理器 2.2.1 80286 微处理器 2.2.2 80386 微处理器 2.2.3 80486 微处理器 2.2.4 Pentium 微处理器

地址加法器 20位 ∑ 8086的内部结构 AH AL BH BL CH CL 8位 CS 通用 寄存器 DH DL DS SP SS 总线 控制逻辑 BP ES DI IP 外部总线 SI 内部暂存器 16位 EU 控制器 1 2 3 4 5 6 ALU 8位 指令队列 总线接口部件 (BIU) 标志寄存器 执行部件 (EU)

8086CPU结构与特点 执行单元EU 2.1.1 总线接口单元BIU 负责与存储器接口,它由段寄存器、指令指针寄存器、指令流队列、地址加法器以及总线控制逻辑组成。 主要负责CPU与存储器之间的信息传送。 ALU 是计算机的运算器 负责执行指令。由算术逻辑单元(Arithmetic Logic Unit,ALU)、通用寄存器组、16位标志寄存器(FLAGS)、EU控制电路等组成。 教学进程

指令队列 指令的一般执行过程: 取指令 指令译码 (前2步合称为取指) 读取操作数 执行指令 存放结果 (最后3步统称指令执行)

串行和并行方式的指令流水线 • 串行工作方式: 控制器和运算器交替工作,按顺序完成 上述指令执行过程。 • 并行工作方式: 运算器和控制器可同时工作。

串行工作方式 • 8088以前的CPU采用串行工作方式: 分析 指令1 执行 指令1 分析 指令2 执行 指令2 CPU 取指令1 取指令2 BUS 忙碌 忙碌

并行工作方式 • 8088CPU采用并行工作方式 分析 指令1 执行 指令1 CPU 取指令1 分析 指令2 执行 指令2 取指令2 分析 指令2 执行 指令2 取指令2 BIU 忙碌 忙碌 忙碌 忙碌 忙碌

3. 8086CPU指令的流水线 • 8086 CPU包括两大部分:EU和BIU • BIU不断地从存储器取指令送入指令队列,EU不断地从指令队列取出指令执行 • EU和BIU构成了一个简单的2工位流水线 • 指令队列是实现流水线操作的关键(类似于工厂流水线的传送带) • 新型CPU将一条指令划分成更多的阶段,以便可以同时执行更多的指令

8086CPU内部寄存器组 通用寄存器(4) 段寄存器(4) 16位寄存器( 14个) 控制寄存器(2) 指针变址寄存器(4) 段寄存器 4 ● CS(Code Segment,代码段寄存器)——存放当前程序所在段的首地址 ● DS(Data Segrnent,数据段寄存器)——保存当前程序所用数据段的首地址 ● SS(Stack Segment,堆栈段寄存器)——存放当前程序所用堆栈段的首地址 堆栈:指一段指定的内存区域:其存取原则是“后进先出”,即先进栈的数据后出栈。 ● ES(Extra Segment附加数据段寄存器)——存放辅助数据所在段的首地址 教学进程

15 8 7 0 AH AL AX 累加器 BH BL BX 基址寄存器 数据寄存器 CH CL CX 计数寄存器 DH DL DX 数据寄存器 15 0 通用寄存器 SP 堆栈指针寄存器 指针寄存器 BP 基址寄存器 SI 源变址寄存器 变址寄存器 DI 目的变址寄存器 15 0 CS 代码段寄存器 DS 数据段寄存器 段寄存器 SS 堆栈段寄存器 ES 附加数据段寄存器 15 0 IP 指令指针寄存器 控制寄存器 FLAGS 状态标志寄存器

存储器分段 • 8086系统存储器分段示意图

逻辑地址 • 段基地址和段内偏移组成了逻辑地址 段地址偏移地址(偏移量) 格式为:段地址:偏移地址 物理地址=段基地址×16+偏移地址 60000H 偏移地址=0002H 60002H 00H 段首地址 12H × × × • • • × × × 0 0 0 0 段基地址(16位)

BIU中的地址加法器用来实现逻辑地址到物理地址的变换BIU中的地址加法器用来实现逻辑地址到物理地址的变换 8088 可同时访问4个段,4个段寄存器中的内容指示了每个段的基地址 16位 段基址 0000 + 段内偏移 物理地址 20位

默认段和偏移寄存器 8086规定了访问存储器段的规则: 此规则定义了段地址寄存器和偏移地址寄存器的 组合方式,其默认规则如下表:

10550H CS CS 250A0H DS 2EF00H ES 8FF00H SS [例]: • 已知CS=1055H,DS=250AH,ES=2EF0H,SS=8FF0H, DS段有一操作数,其偏移地址=0204H, 1)画出各段在内存中的分布 2)指出各段首地址 3)该操作数的物理地址=? 解: 各段分布及段首址见右图所示。 操作数的物理地址为: 250AH×10H+0204H = 252A4H 这个例子说明:段与段可以不连续 段之间可以重叠

存储器分段 逻辑地址和物理地址 ⑴ 逻辑地址:由段地址(逻辑段起始地址的高16位)和偏移地址(16位)表示的存储单元的地址称为逻辑地址,记为: 段地址∶偏移地址 ⑵ 物理地址:由CPU内部总线接口单元BIU中的地址加法器根据逻辑地址产生的20位存储单元地址称为物理地址。

15 0 物理地址和逻辑地址的关系为: 物理地址=段地址×10H+偏移地址 在程序设计中,段地址是由段寄存器(如CS、DS、SS或ES)提供,偏移地址通常是由地址寄存器(如IP、BX、BP、SP、SI或DI等)及立即数等提供。 段内偏移地址 19 4 3 0 段寄存器 0000 段地址左移4位 ∑ 19 0 20位物理地址 物理地址的形成

M 00000H A段 紧密相连 64KB 部分重叠 完全重叠 10000H B段 64KB 1FF00H C段 D段 20000H 64KB 2FEFFH 64KB 30000H E段 断开排列 64KB 40000H

对于任何一个物理地址来说,可以唯一被包含在一个逻辑段中,也可以包含在多个重叠的逻辑段中,只要能得到它所在段的首地址和段内的相对地址,就可以对它进行访问。即一个物理地址可以对应多个逻辑地址。对于任何一个物理地址来说,可以唯一被包含在一个逻辑段中,也可以包含在多个重叠的逻辑段中,只要能得到它所在段的首地址和段内的相对地址,就可以对它进行访问。即一个物理地址可以对应多个逻辑地址。 偏移地址 物理地址 段基址: 11230H 11231H 11232H 1123H 0000H 0001H 0002H 1123H×16+15H=11245H … 1124H×16+05H=11245H 15H 000EH 000FH 0010H 0011H 0012H 0013H 0014H 0015H 1123EH 1123FH 11240H 11241H 11242H 11243H 11244H 11245H 段基址: 1124H 05H … 1122EH 1122FH FFFEH FFFFH

(2) 通用数据寄存器 BX(Base):基址寄存器 AX(Accumulator):累加器 CX(Count):计数寄存器 DX(Data):数据寄存器 (3) 地址寄存器 SP(Stack Pointer)堆栈指针寄存器 BP(Base Pointer)基址指针寄存器 SI(Source Index)源变址寄存器 Dl(Destination Index)目的变址寄存器 ● 用来暂存操作数,每个寄存器可作为一个16位的寄存器使用,也可分成2个8位寄存器使用:AX→AH,AL BX →BH,BL CX→CH,CL DX →DH,DL ● 习惯用法 教学进程

指令指针寄存器 状态标志寄存器 6个状态标志——表示运算结果的特征 ● PSW定义了9个有效位,存放 3个控制标志——用来控制CPU的操作 2.1 8086微处理器 8086 CPU结构与特点 2.1.1 ● IP(Instruction Pointer):取指专用的16位地址寄存器,也称为“程序 计数器”PC(Program Counter),存放下一条要执行指令的有效地址 EA(即偏移地址)。 ● FR(Flag Register):16位的寄存器,存放状态字PSW(Program status Word),又称状态字寄存器。 OF SF ZF AF PF CF DF IF TF 教学进程

状态标志寄存器 1 CF(Carry Flag)进位标志 2 PF(Parity Flag)奇偶校验标志 AF(Auxiliary Carry Flag)辅助进位标志 3 4 5 6 ZF(Zero Flag)零标志 OF(Overflow Flag)溢出标志 SF(Sign Flag)符号标志 表示执行一次加法/减法运算时产生了进位/借位,当算术运算结果使最高位产生进位或借位时,则CF=1,否则CF=0。 当本次运算结果中的低8位含“1”个数为偶数时,PF=1,为奇数时PF=0。 本次运算中若第3位向第4位有进位或借位时,AF=1,否则, AF=0。 若本次运算结果为0时,ZF=1,否则,ZF=0。 若本次运算结果的最高位为1,则SF=1,否则,SF=0 当带符号数运算结果产生溢出时,OF=1。 教学进程

8086CPU引脚功能 地址/状态线 地址/数据线 最小最大模式控制 MN/MX=1,最小模式 MN/MX=0,最大模式 读信号 总线保持请求信号 总线保持相应信号 存储器/IO控制信号 M/IO=1,选中存储器 M/IO=0,选中IO接口 写信号 数据发送/接收信号 DT/R=1,发送 DT/R=0,接收 数据允许信号 地址允许信号 非屏蔽中断 中断响应信号 准备好信号:表示内存 或I/O设备准备好, 可以进行数据传输。 测试信号:执行WAIT指令, CPU处于空转等待; TEST有效时,结束等待状态。 可屏蔽中断请求 复位信号

8086的工作模式及引脚功能 VCC(5V) AD15 AD16/S2 AD17/S4 AD18/S5 AD19/S6 BHE/S2 MN/MX RD HOLD(RQ/GT0) HLDA(RQ/GT1) WR(LOCK) M/IO(S2) DT/R(S1) DEN(SD) ALE(QSD) INTA(QS4) TEST READY RESET 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 地 AD14 AD13 AD12 AD11 AD10 AD9 AD8 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 NMI INTR CLK 地 8086CPU 2.1 8086的结构特点 2.1.2 8086的工作模式和引脚特性 当CPU工作在不同模式时,引脚具有不同的名称和定义。 但是还有部分公用引脚在不同模式下具有相同的含义。 教学进程

公用引脚的含义 8086的工作模式及引脚功能 2.1.3 外部引脚及功能 ● 教学进程

最小模式下的部分引脚含义 引脚 功 能 INTA 为中断响应输出端 ALE 地址锁存允许信号,三态输出,高电平有效 DEN 数据允许信号,三态,低电平有效 DT/R 数据传送方向控制信号,三态。用于确定数据传送的方向 M/IO 输入/输出/存储器控制信号,三态 WR 写信夸输出,三态 HOLD 总线保持请求信号输入,高电平有效 HLDA 总线保持响应信号输出,高电平有效 8086的工作模式及引脚功能 ● 引脚24~31在最小模式下的功能 教学进程

最大模式下的部分引脚含义 当 MN/MX 引脚为低电平时,8086工作在最大模式下 引脚 功能 总线周期状态信号输出,低电平有效,三态 S2 , S1 , S0 指令流队列状态输出 QS1 QS0 总线封锁信号输出,低电平有 LOCK 总线请求/总线响应信号引脚。每一个引脚都具有双向功能,既是总线请求输入,也是总线响应输出 RQ/GT0 RQ/GT! 8086的工作模式及引脚功能 ● 教学进程

8086的总线操作和时序 总线周期 总线周期 T1 T2 T3 T4 T1 T2 T3 TW T4 地址 缓存 数据 地址 缓存 数据 2.1.3 2.2.1 基本时序 ● 总线操作主要有:存储器读和I/O读操作、存储器写和I/O写操作、 中断响应操作、总线请求等。 ●CPU的时序分为两种:时钟周期和总线周期 。 ● CPU通过总线对存储器或I/O接口进行一次访问所需的时间叫做 一个总线周期,一条指令的执行需要若干个总线周期才能完成。 而一个总线周期又由若干个时钟周期构成。 ● 典型的总线周期如图: 教学进程

8086CPU的工作时序 2.1.3 2.2.1 80286微处理器 ● 8086的数据总线和部分地址总线是分时复用的。在一个总线周期 内,先利用总线传送地址,将地址锁存后,再利用同一总线传送 数据。 ●在两个总线周期之间,有时可能会出现一些总线上没有信息传送 的时钟周期,此时的总线状态称为空闲状态。 教学进程

80386 微处理器 CPU的20根地址信号线通过3片8282锁存器与系统的地址总线相连。 小系统所需的全部控制信号由CPU直接产生,可直接接入总线。 2.2.2 2.2 8086CPU的工作时序 ● 1.工作电路 8086在最小模式下的系统构成 16位数据线通过两片8286双向总线驱动器连接到系统的数据总线上。 教学进程

BHE DEN DT / R M / IO INTA RD WR V (+5 V) V CC CC MN / MX 8284A CLK ALE STB 时钟发生器 READY 地址锁存器 RESET 8282 地址总线AB ~ RDY A /S A /S (3片) 19 6 16 3 ~ AD AD OE 15 0 等待状态 数据收发器 8086 CPU 产生器 8286 数据总线DB (2片) INTR 控制总线CB HOLD HLDA 图 8086最小方式系统结构

A F A F A F A F T T T 表示反相或低电平有效 T 三态缓冲器(三态门) 具有单向导通和三态的特性 T为低平时: 输出为高阻抗(三态) T为高电平时: 输出为输入的反相

常用接口芯片介绍 74LS244 双4位单向缓冲器 • 分成4位的两组 • 每组的控制端连接在一起 • 控制端低电平有效 • 输出与输入同相 每一位都是一个三态门, 每4个三态门的控制端连接在一起

A B T OE* 双向三态缓冲器 具有双向导通和三态的特性 OE*=0,导通 T=1 A→B T=0 A←B OE*=1,不导通

常用接口芯片介绍Intel 8286 8位双向缓冲器 • 控制端连接在一起, 低电平有效 • 可以双向导通 • 输出与输入同相 OE*=0,导通 T=1 A→B T=0 A←B OE*=1,不导通 每一位都是一个双向三态门, 8位具有共同的控制端

常用接口芯片介绍74LS245 8位双向缓冲器 • 控制端连接在一起, 低电平有效 • 可以双向导通 • 输出与输入同相 E*=0,导通 DIR=1 A→B DIR=0 A←B E*=1,不导通 74LS245与Intel 8286功能一样

D Q C Q 电平锁存 S D Q C Q D Q C Q 上升沿锁存 R D触发器 电平锁存: 高电平通过,低电平锁存 上升沿锁存: 通常用负脉冲触发锁存 负脉冲的上升沿 带有异步置位清零的 电平控制的锁存器

常用接口芯片介绍 74LS273 具有异步清零的 TTL上升沿锁存器 每一位都是一个D触发器, 8个D触发器的控制端连接在一起

锁存环节 缓冲环节 三态缓冲锁存器(三态锁存器) A B D Q C T

Q Q Q D D D CLK CLK CLK 常用接口芯片介绍带三态缓冲的8位数据锁存器8282 DI0 DO0 DO1 DI1 STB:选通脉冲 OE:为0时输出有效 为1时输出为高阻 DI7 DO7 8282内部结构图 STB OE

Intel 8282 具有三态输出的 TTL电平锁存器 STB 电平锁存引脚 OE* 输出允许引脚 每一位都是一个三态锁存器, 8个三态锁存器的控制端连在一起

常用接口芯片介绍 74LS373 具有三态输出的 TTL电平锁存器 LE 电平锁存引脚 OE* 输出允许引脚 74LS373与Intel 8282功能一样

最大模式 • 最大模式——可支持多处理器 • 大多数控制信号是由总线控制器8288对S0#、S1#、S2#三个信号译码得到,如DT/R#、ALE、DEN#、IOR#、IOW#、MEMR#、MEMW#信号。DB和AB的构成基本同最小模式。 • PC/XT机的总线采用了最大模式,但有三点区别: • 地址总线驱动用2个74LS373和1个74LS244代替3个8282; • 数据总线驱动用74LS245代替8286; • 支持DMA传送。

AEN IOB S S MRDC 0 0 S S MWTC 1 1 S AMWC S 2 2 IORC DT / R IOWC AIOWC INTA BHE MN / MX OE +5 V V CC CLK CEN CLK 8288 8284A READY 总线 时钟发生器 RESET 控制器 控制总线CB DEN ALE 等待状态 8086 CPU 产生器 STB 地址锁存器 8282 地址总线AB A /S A /S 16 3 19 6 (3片) AD AD OE 15 0 数据收发器 T 8286 数据总线DB (2片) 1 图 8086最大方式系统结构

常用接口芯片介绍 8286(或74LS245)是8位总线驱动器(双向) T是控制收发方向的输入控 制信号: T=1,A→B; T=0,B→A; OE=0,输出允许信号; OE=1,8086是高阻。 8286可以提供32mA驱动。 A0~A7 B0~B7 DEN OE DT/R T

常用接口芯片介绍带三态的8位双向数据缓冲器8286常用接口芯片介绍带三态的8位双向数据缓冲器8286 A0 B0 A1 B1 A7 B7 8286内部结构图 OE T

80x86微处理器及其发展 2.3 2.3.1 80286微处理器 ● 主要性能 80286微处理器为16位微处理器。对外具有68根引脚,为4列直插式封装,时钟频率8MHz~10MHz。 80286CPU与8086相比,主要具有如下几个特点: ① 80286 CPU有24位地址线、16位数据线,且地址与数据线不再复用。 ② 对8086向上兼容。具有8086/8088 CPU的全部功能。 ③ 首次具备虚拟存储器管理功能。 教学进程 教学进程

80286微处理器 地址单元 AU 24位 物理地址 24位地址总线 16位偏移量或数据 存储器 操作请求 16位数据总线 物理地址发生器 通用寄存器组 总线接口电路 总线接口单元BIU 段寄存器 ALU标志寄存器 执行单元EU 指令单元IU 段描述符Cache 预取器 控制电路 指令预取队列 指令译码器 译码的指令队列 2.3.1 2.3 80x86微处理器及其发展 ● 内部结构 80286 CPU的内部执行部件包括:执行单元EU、地址单元(Addres Unit,AU)、指令单元(Istruction Unit,IU)和总线接口单元BIU。 教学进程 教学进程