IRS

IRS. INTEGRISANI RAČUNARSKI SISTEMI PART 4. Autor : Nenad Jovičić. Projektni zadatak 4.

IRS

E N D

Presentation Transcript

IRS INTEGRISANI RAČUNARSKI SISTEMI PART 4 Autor: NenadJovičić

Projektnizadatak4 Napisatiasemblerskiprojekatza razvojni sistem RS-MSP430F449 kojisvake sekunde obezbeđuje inkrementiranje jedne decimalne cifre u registru R10 i njen ispis na statički nemultipleksirani LCD. Za merenje vremena koristiti prekid tajmera A sa periodom 1s. Glavni program treba da ima funkciju osvežavanja displeja.

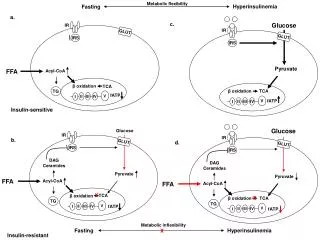

LCD kontroler • LCD memorijazasegmente • Softverskopodešavanjeučestanostiosvežavanja • Mogućnostradasačetirivrste LCD displeja: • statički • sadvostrukimmultipleksiranjem • satrostrukimmultipleksiranjem • sačetvorostrukimmultipleksiranjem • Mogućnostautomatskogblinkovanja

LCD memorija • Svaki bit u memoriji odgovara određenom segmentu

MSP430_RS – faktičko stanje na ploči Preslikavanje iz LDC memorije na displej zavisi od toga kako je displej fizički povezan sa mikrokontrolerom.

DMA kontroler • Osnovnekarakteristike: • do 3 nezavisnakanala, • prenos bajta ili reči, • prenos traje samo dve MCLK periode, • prenos pojedinačnih podataka ili blokova podataka, • mnoštvo različitih događaja koji mogu startovati prenos.

DMA - prekidi Svaki kanal DMA kontrolera može da generiše prekid. Prekid se generiše nakon završetka prenosa. Iako svaki kanal ima mogućnost individualnog maskiranja prekida, svi prekidi DMA kontrolera kao i prekidi DAC12 modula dele isti prekidni vektor.