Microarchitecture of Superscalars (8) Basic Processor Structures

Microarchitecture of Superscalars (8) Basic Processor Structures. Dezső Sima Fall 2007. (Ver. 2.0). Dezső Sima, 2007. Overview. 1. Overview. 2. Dynamic instruction issue. 3. Predecoding. 2.1 Significant design aspects of dynamic instruction issue. 2.2 Basic issue schemes.

Microarchitecture of Superscalars (8) Basic Processor Structures

E N D

Presentation Transcript

Microarchitecture of Superscalars (8)Basic Processor Structures Dezső Sima Fall 2007 (Ver. 2.0) Dezső Sima, 2007

Overview 1. Overview 2. Dynamic instruction issue 3. Predecoding 2.1 Significant design aspects of dynamic instruction issue 2.2Basic issue schemes 3.Register renaming 3.1 Significant design aspects of register renaming 3.2Basic renaming schemes 4. Basic processor structures

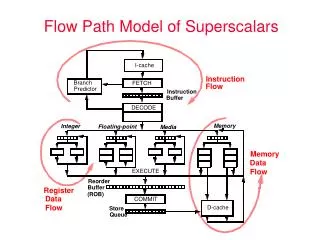

1. Overview (1) Basic structure: The microarchitecture needed for executing FX/FP instructions It depends on: • instruction fetching • decoding • instruction dispatching • dynamic instruction issue • register renaming • instruction issue • execution • data operations • branches • load/store instructions • writing results into registers/memory

1. Overview (2) Possible basic structures Derived from the design spaces of dynamic instruction issue and register renaming Defined by the relevant design aspects

2. Dynamic instruction issue 2.1 Significant design aspects of dynamic instruction issue (1) Dynamic instruction issue Scope of dynamic instr. issue Instruction issue scheme Layout of the issue buffers Operand fetch policy Types of issue buffers

2.1 Significant design aspects of dynamic instruction issue (2) RS FP EU RS RS FX FP RS RS FX EU FX EU FP EU FX EU FP EU FX EU FX EU FX EU FX EU Types of issue buffers Issue buffers in the ROB Reservation stations (RS) Individual RSs Central RS Group RSs Power1 (1990) PowerPC 603 (1993) PowerPC 604 (1995) Power4 (2001) Power5 (2004) K5 (1995) K7 (1999), K8 (2003) ES/9000 (1992) Power2 (1993) R10000 (1996) PM1(Sparc64)(1995) Alpha 21264 (1997) Pentium Pro (1995) Pentium II (1997) Pentium III (1999) Pentium 4 (2000) Pentium M (2003) Core (2006) Lightning (1991)p K6 (1997)

2.1 Significant design aspects of dynamic instruction issue (3) Dynamic instruction issue Scope of buffered issue Instruction issue scheme Layout of the issue buffers Operand fetch policy Types of issue buffers

2.1 Significant design aspects of dynamic instruction issue (4) Rs1 Rs2 IB IB Rd Op2/Rs2 Op1/Rs1 Operand fetch policies Issue bound operand fetch policy Dispatch bound operand fetch policy I-buffer I-buffer Decode / Issue Decode / Issue Source reg. identifiers Source reg. identifiers Dispatch Dispatch Reg. file IB IB Issue Opcodes, destination reg. identifiers OC Rd OC Rd Rs1 Rs2 Source 1 operands Source reg. identifiers Source 2 operands Opcodes, destination reg. identifiers Reg. file Issue Source 1 operands OC OC Rd Op1/Rs1 Op2/Rs2 Source 2 operands EU EU EU EU Rd, result Figure 2.1: Operand fetch policies

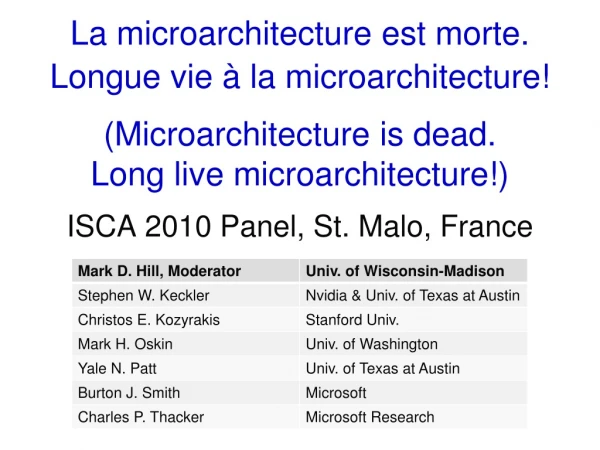

2.2 Basic issue schemes Basic issue schemes Issue buffers in the ROB Reservation stations (RS) Types of issue buffers Individual RSs Central RS Group RSs Dispatch bound Issue bound Dispatch bound Issue bound Dispatch bound Issue bound Dispatch bound Issue bound Operand fetch policy PowerPC 603 (1993) PowerPC 604 (1995) K5 (1995) PM1(Sparc64)(1995) Pentium Pro (1995) Pentium II (1997) Pentium III (1999) POWER1 (1990) POWER4 (2001) POWER5 (2004) Nx586 (1994) K7 (1999), K8 (2003) ES/9000 (1992) POWER2 (1993) R10000 (1996) Alpha 21264 (1997) Pentium 4 (2000) Pentium M (2003) Core (2006) Lightning (1991)p K6 (1997)

3. Register renaming 3.1 Significant design aspects of register renaming (1) Register renaming Scope of register renaming Rename rate Layout of the rename buffers Layout of the register mapping Type of rename buffers

3.1 Significant design aspects of register renaming (2) Types of rename buffers Rename reg. file Merged arch. and rename register file Holding renamed values in the ROB Future file Reg. nrs. Reg. nrs. Reg. nrs. Reg. nrs. ROB Res. Res. AR Ret. Res. Res. FF Ret. Ret. AR AR AR, RR RR Ops. Ops. Ops. Ops. POWER1 (1990) POWER2 (1993) R10000 (1996) R12000 (1999) Alpha 21264 (1998) Pentium 4 (FP) (2000) K7 (FP) (1999) K8 (FP) (2003) K5 (1995) K6 (1997) Pentium Pro (1995) Pentium II (1997) Pentium III (1999) Pentium 4 (FX) (2000) Pentium M (2003) Core (2006) PowerPC 603 (1993) PowerPC 604 (1995) PowerPC 620 (1996) POWER3 (1998) PA 8000 (1996) PA 8200 (1997) PA 8500 (1999) UltraSPARC III (1999) K7 (FX) (1999) K8 (FX) (2003)

3.2 Basic renaming schemes Types of rename buffers Types of ren.buffers Rename reg. file Merged arch. and rename register file Holding renamed values in the ROB Future file Op. fet. poli. Dispatch bound Issue bound Dispatch bound Issue bound Dispatch bound Issue bound Dispatch bound Issue bound Smith, Pleszkun, (85) Proposals Johnson (87) Keller (75) Sohi,Vajapeyam (87) PowerPC 603 (93) K7 (FX) (99) PM1 (95) ES/9000 (92) Pentium Pro (95) K8 (FX) (03) (SPARC 64) POWER1 (90) Pentium II (97) PowerPC 604 (95) Pentium III (99) POWER2 (93) PowerPC 620 (96) UltraSPARC III (99) Pentium M (03) P2SC (96) Core (06) POWER4 (01) POWER3 (98) Examples POWER5 (04) PA 8000 (96) Nx586 (94) Am29000 (95) PA 8200 (97) R10000 (96) K5 (95) PA 8500 (99) R12000 (99) Lightning* (91) Pentium 4 (00) K6* (97) K7 (FP) (99) K8 (FP) (03)

4. Basic processor structures (1) Basic issue schemes Reservation stations (RS) Issue buffers in the ROB Type of issue buffers Individual RSs Group RSs Central RS Op.fetch policy Dispatch bound Issue bound Dispatch bound Issue bound Dispatch bound Issue bound Dispatch bound Issue bound Rename reg file Future file Type of rename buffers Merged file Ren. in ROB

Decode/Dispatch. d d s1, s2 s1, s2 FX- mapping table FP- mapping table d’ s1/s1’, s2/s2’ d’ s1/s1’, s2/s2’ FX-group reservation station FP-group reservation station d’ s1/s1’, s2/s2’ s1/s1’, s2/s2’ Merged FP-reg. file Merged FX-reg. file d’ d’ d’ d’ o1, o2 o1, o2 FX-EU FX-EU FP-EU FP-EU d’ r, d’ d’ r, d’ ROB Figure 4.1: Group reservation station, issue bound operand fetching,split, merged architectural and register files (R10000, Alpha21264)

4. Basic processor structures (2) Basic issue buffer schemes Reservation stations (RS) Issue buffers in the ROB Type of issue buffers Individual RSs Group RSs Central RS Op.fetch policy Dispatch bound Issue bound Dispatch bound Issue bound Dispatch bound Issue bound Dispatch bound Issue bound PA-8000 PA-8200 PA-8500 PPC603 PPC604 PPC620 POWER3 Rename reg file K7 (FX) K8 (FX) UltraSPARCIII Future file Type of rename buffers POWER2 R10000 Alpha21264 Pentium4 (FP) Nx586 POWER1 POWER4 POWER5 PM1 Merged file K7, K8 (FP) Pentium 4 PentiumPro Pentium II Pentium III Pentium4 (FX) Pentium M Core Lightning K6 Am 2900 supersc. K5 Ren. in ROB