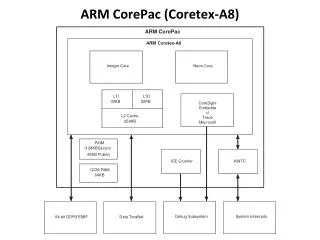

ARM CorePac (Coretex-A8)

ARM CorePac. ARM Coretex-A8. Integer Core. Neon Core. L1I. L1D. 32KB. 32KB. CoreSight Embedded Trace Macrocell. L2 Cache. 256KB. ROM. (128KB. Secure. 48KB Public). ICE Crusher. AINTC. OCM RAM. 64KB. Debug Subsystem. System Interrupts. 64-bit DDR3 EMIF. Data TeraNet.

ARM CorePac (Coretex-A8)

E N D

Presentation Transcript

ARM CorePac ARM Coretex-A8 Integer Core Neon Core L1I L1D 32KB 32KB CoreSight Embedded Trace Macrocell L2 Cache 256KB ROM (128KB Secure 48KB Public) ICE Crusher AINTC OCM RAM 64KB Debug Subsystem System Interrupts 64-bit DDR3 EMIF Data TeraNet ARM CorePac (Coretex-A8)

ARM Coprocessors 64-Bit Cortex-A8 2MB DDR3 EMIF MSM 32KB L1 32KB L1 SRAM RAC Memory P-Cache D-Cache • x2 MSMC Subsystem 256KB L2 Cache TAC Debug & Trace RSA RSA x2 Boot ROM VCP2 • x4 Semaphore C66x™ Power TCP3d CorePac Management • x2 PLL FFTC • x2 32KB L1 32KB L1 x3 P-Cache D-Cache EDMA 1024KB L2 Cache BCP x3 Cores @ 1.0 GHz / 1.2 GHz HyperLink TeraNet Multicore Navigator Queue Packet Manager DMA t x2 x2 x6 6 x4 e h 1 M n I c T C r I Security P h F t e O i 2 S e I R c 2 I S Accelerator I I w F h t M U C A R I i t S E P A w U S E S Packet Accelerator I I M x2 G S Network Coprocessor TCI6614 TCI6614 Functional Architecture