AFEII for MICE

150 likes | 221 Vues

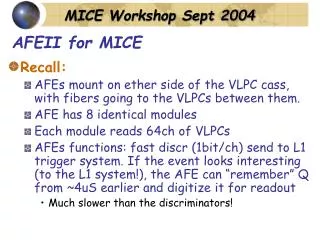

AFEII for MICE. Recall: AFEs mount on ether side of the VLPC cass, with fibers going to the VLPCs between them. AFE has 8 identical modules Each module reads 64ch of VLPCs

AFEII for MICE

E N D

Presentation Transcript

AFEII for MICE • Recall: • AFEs mount on ether side of the VLPC cass, with fibers going to the VLPCs between them. • AFE has 8 identical modules • Each module reads 64ch of VLPCs • AFEs functions: fast discr (1bit/ch) send to L1 trigger system. If the event looks interesting (to the L1 system!), the AFE can “remember” Q from ~4uS earlier and digitize it for readout • Much slower than the discriminators!

AFEII for MICE • Digital readout vs. Analog readout • AFEII two readout paths • Digital: Discriminators go over LVDS links • More details later • Analog:Zero suppressed data from ADCs (addr/data pairs) over a custom parallel link (a.k.a. gray cable) • More details later

AFEII for MICE • AFEII designed for Tevatron not MICE! • AFEII two readout paths: • L1: 512 discriminator bits/board/132ns • L2: (only after an “L1 accept”) reads out ADC8bits/ch x 512ch (zero supressed) • AFEII designed for ~10Khz L1 accept rate at ~5% deadtime => 10uS per event time budget

AFEII for MICE • Fiber tracker: why analog at all? • Better quality data • ADCs data can be corrected for common mode • ADCs can correct for ch-to-ch variation • But watch out for zero supression! • For Dzero, can use to improve resolution

AFEII for MICE • Digital readout details: • LVDS here means a specific chip set from TI • SN65LVDS95 (running @ 53Mhz) • 20 bits + 1 “frame” bit sent over 4 UTP pairs (3 signal + clock) @ 53 * 7 = 371 Mhz • Frame bit sent once every 7 * 18.8ns = 132ns • 4 LVDS links/board = 1/pair of modules (10bits per module) Data rate = 53Mhz * 20 * 4 = 4.24 Gbps

AFEII for MICE • Analog readout details: • Custom bi-directional parallel link between the Sequencer and the AFE • 8 data bits + data valid per AFE Max data rate = 53 * 8 = 424 Mbps • Digitization: • 2 dual ADCs/64 ch module=16 ch/ADC • ADC runs @ max 10Mhz => 16 * 100ns = 1.6uS • Tot: ~2us + ~40ns / hit ch= ~21us max

AFEII for MICE • Mice beam structure ~600 muons in 850 uS • Long enough between pulses = for DAQ • Analog readout: depends on occupancy • If FULL readout, can do about ~40 during spill • Digital readout: can keep up • Still not 100% live time: need resets us

AFEII for MICE • Mice readout • Analog readout for MICE Two options: 1. the full Dzero system -Sequncer (SEQ) and sequencer controller (SEQC) (and crate! 9U custom backplane…) - VME Receiver Buffer (VRB) and VRB controller (VRBC) (and another 9U crate!) - must talk to SEQ/SEQC/VRB/VRBC so need 1553 interface as well

AFEII for MICE • Mice readout (cont.) • Analog readout for MICE Two options: 2. the StandAlone Sequencer (SASeq) +used in the MICE cosmic test -rather slow…

AFEII for MICE • Analog readout for MICE + tons of experience from Dzero + AFEII designed to work this way + know how to trigger, sync board to board, etc. • need time to digitize! ~ maybe beam structure can be chosen to make this mode work better? 600mu/1ms => 600KHz L1 accept rate!

AFEII for MICE • Mice readout • Digital readout for MICE + fast + very simple - need a receiver… more detail below - no detailed analog info ~ not for use with AFEII-t (not a problem!)

AFEII for MICE • Digital readout for MICE • Need a new board! • Receive LVDS, store into FIFO, interface to VME • But • How to get clock to boards? • How to get trigger to board? Can still use the gray cable! (w/SASeq)

SRAM VME I/F FPGA LVDS AFEII for MICE • Need new board • Very simple 6U VME • Should be easy for a strong group (like IC) to design and build! • Cost=$1K/board • 1 board/AFE

AFEII for MICE • Hybrid option • On the AFEII, there is a path from FPGA to LVDS • Can readout analog information via LVDS • Still need the digitize time =~1.6 to 2 us • But can readout as fast as digitize

AFEII for MICE summary • Analog readout • Maybe 40 events/pulse (if 850uS pulse!) • Digital readout • Trade live time vs. overlaps (2K events/pulse) • Min integration window ~50ns, max=anything! • Reset time ~40ns • Need to design and build a new board! • Hybrid readout • ADC thru LVDS (400 events/pulse) • Still need the new board!