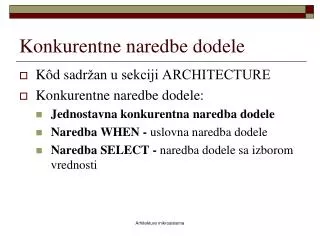

Konkurentne naredbe dodele

Konkurentne naredbe dodele. Kôd sad ržan u sekciji ARCHITECTURE Konkurentne naredbe dodele : Jednostavna konkurentna naredba dodele Naredba WHEN - uslovna naredba dodele Naredba SELECT - naredba dodele sa izborom vrednosti. Jednostavna konkurentna nareba dodele. signal <= izraz;

Konkurentne naredbe dodele

E N D

Presentation Transcript

Konkurentne naredbe dodele • Kôd sadržan u sekciji ARCHITECTURE • Konkurentne naredbe dodele: • Jednostavna konkurentna naredba dodele • Naredba WHEN - uslovna naredba dodele • Naredba SELECT - naredba dodele sa izborom vrednosti Arhitekture mikrosistema

Jednostavna konkurentna nareba dodele • signal <= izraz; • izraz – logički ili aritmetički izraz (sadrži operatore AND, NOT, +, sll i sl.) • s<= a AND (b OR c); • enable <= ´1´; • sel <= (r1 AND r2) OR (r3 AND r4); • sum <= a + b + c – 1; • Za opis jednostavnih logičkih i aritmetičkih funkcija Arhitektura mikrosistema

Jednostavna konkurentna nareba dodele • Jednostavna konkurentna naredba dodele sa klauzulom after: • signal <= izraz afterkašnjenje; • a <= b AND c after 10 ns; • Koristi se u simulaciji. U sintezi niji dozvoljen. Arhitektura mikrosistema

Generisanje talasnog oblika sig <= ´0´, ´1´ after 10 ns, ´0´ after 10 ns, ´1´ after 20 ns; Tipična primena u testbenču za generisanje pobudnih signala složenog talasnog oblika Arhitektura mikrosistema

Konceptualna implementacija konkurentne naredbe dodele • enable <= ´1´; • sel <= (r1 AND r2) OR (r3 AND r4); • sum <= a + b + c – 1; Arhitektura mikrosistema

Konkurentna nareba dodelePrimer: multiplekser 4-u-1 LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY mux IS PORT ( a,b,c,d,s0,s1 : IN STD_LOGIC; y : OUT STD_LOGIC); END mux; ARCHITECTURE log_funk OF mux IS BEGIN y <= (a AND NOT s1 AND NOT s0) OR (b AND NOT s1 AND s0) OR (c AND s1 AND NOT s0) OR (d AND s1 AND s0); END log_funk; Nizak nivo opisa Arhitektura mikrosistema

WHEN - konkurentna naredba uslovne dodele • Uopštenje konkurentne naredbe dodele • S desne strane znaka <= može se naći više od jednog izraza. • Sintaksa: sig <= izraz_1 WHEN uslov_1 ELSE izraz_2 WHEN uslov_2 ELSE ... izraz_n-1 WHEN uslov_n-1 ELSE izraz_n; • ˝uslov˝ - logički/relacioni izraz koji može biti tačan ili netačan, npr: (a OR b) ili (a> b) • ˝uslovi˝ se ispituju redom, a signal dobija vrednost prvog izraza čiji je uslov tačan • Ako ni jedan uslov nije tačan, izvršava se izraz iz poslednje grane Arhitektura mikrosistema

WHEN - primer • outp <= “000” WHEN (inp=΄0΄ OR reset=΄1΄) ELSE • “101” WHEN ctl=΄1΄ ELSE • “010”; Ako važi inp=΄0΄ ili reset=΄1΄, tada outp <= “000”, inače ako važi ctl=΄1΄ , tada outp <= “101”, inače outp <= “010” Arhitektura mikrosistema

WHEN Primer: Multiplekser LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY mux IS PORT ( a,b,c,d : IN STD_LOGIC; sel: IN STD_LOGIC_VECTOR(1 DOWNTO 0); y : OUT STD_LOGIC); END mux; ARCHITECTURE when_arch OF mux IS BEGIN y <= a WHEN sel = "00" ELSE b WHEN sel = "01" ELSE c WHEN sel = "10" ELSE d; END when_arch; Pokriva sel=˝11˝, ali i sve preostale, nebinarne kombinacije, kao što su ˝0-˝, ˝LH˝, ˝ZW˝ Arhitektura mikrosistema

WHEN Primer: Dekoder LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY dek2u4 IS PORT (d : IN STD_LOGIC_VECTOR(1 DOWNTO 0); e : IN STD_LOGIC; y : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END dek2u4; ARCHITECTURE when_arch OF dek2u4 IS BEGIN y <= "0000" WHEN e = ´0´ ELSE "0001" WHEN d = "00" ELSE "0010" WHEN d = "01" ELSE "0100" WHEN d = "10" ELSE "1000"; END when_arch; Arhitektura mikrosistema

WHEN Primer: Koder LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY encoder IS PORT (x : IN STD_LOGIC_VECTOR(3 DOWNTO 0); y : OUT STD_LOGIC_VECTOR(1 DOWNTO 0)); END encoder; ARCHITECTURE when_arch OF encoder IS BEGIN y <= "00" WHEN x="0001" ELSE "01" WHEN x="0010" ELSE "10" WHEN x="0100" ELSE "11"; END when_arch; Arhitektura mikrosistema

WHEN Primer: Prioritetni koder LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY pencoder IS PORT (x : IN STD_LOGIC_VECTOR(3 DOWNTO 0); y : OUT STD_LOGIC_VECTOR(1 DOWNTO 0); z : OUT STD_LOGIC); END pencoder; ARCHITECTURE when_arch OF pencoder IS BEGIN y <= "11" WHEN x(3) = '1' ELSE "10" WHEN x(2) = '1' ELSE "01" WHEN x(1) = '1' ELSE "00"; z <= '0' WHEN x = "0000" ELSE '1'; END when_arch; Arhitektura mikrosistema

Konceptualna implementacija WHEN naredbe sig <= izraz_1 WHEN uslov_1 ELSE izraz_2; Apstraktni multiplekser: T (true) - uslov je tačan F (false) - uslov je netačan Konceptualni dijagram Arhitektura mikrosistema

Konceptualna implementacija WHEN naredbe sig <= izraz_1 WHEN uslov_1 ELSE izraz_2 WHEN uslov_2 ELSE izraz_3 WHEN uslov_3 ELSE izraz_4; Arhitektura mikrosistema

Sinteza WHEN naredbe SIGNAL a,b,y : STD_LOGIC; . . . y <= ´0´ WHEN a=b ELSE ´1´; . . . U sintezi STD_LOGIC ima dve vrednosti: ‘0’ i ‘1’ U sintezi T - ‘1’, F - ‘0’ Arhitektura mikrosistema

Konceptualna implementacija WHEN naredbe - primer SIGNAL a,b,f : UNSIGNED(7 DOWNTO 0); SIGNAL x,y : UNSIGNED(3 DOWNTO 0); . . . f <= a+b WHEN x+y>1 ELSE a-b-1 WHEN x>y AND y!=0 ELSE a+1; . . . Nije kraj sinteze ! Sledi zamen apstraktnih blokova Odgovarajućim modulima realizovanim pomoću logičkih kola Arhitektura mikrosistema

SELECET - naredba dodele sa izborom vrednosti • Sintaksa: WITH selekcioni_izraz SELECT sig <= izraz_1 WHEN vrednost_1, izraz_2 WHEN vrednost_2, ... izraz_n WHEN vrednost_n; • selekcioni_izraz –aritmetički ili logički izraz • Izračunata vrednost selekcioni_izraz, poredi se sa vrednostima iz svih grana, a signal dobija vrednost izraza iz grane gde se javilo slaganje. • Zahtev: svaka moguća vrednost selekcionog_izraza mora biti pokrivena tačno jednom granom. • ˝WHEN vrednost˝ može biti: • WHEN vrednost; -- jedinstvena vrednost • WHEN vrednost_1 TO vrednost_2; -- opseg vrednosti • WHEN vrednost_1 | vrednost_2 | vrednost_3 ... -- više vrednosti Arhitektura mikrosistema

SELECT • Dozvoljeno korišćenje reči OTHERS: WITH selekcioni_izraz SELECT sig <= izraz_1 WHEN vrednost_1, izraz_2 WHEN vrednost_2, ... izraz_n WHEN OTHERS; • Primer: WITH contol SELECT outp <= “000” WHEN “00” “111” WHEN “01” | “10” “010” WHEN OTHERS; Bira se ako vrednost selekcionog izraza nije jednaka ni jednoj navedenoj vrednosti Arhitektura mikrosistema

Realizacija tabele istinitosti Arhitektura mikrosistema

OTHERS grana je neophodna kad se radi s tipom std_logic ! tmp <= a & b; WITH tmp SELECT y <= '0' WHEN "00", '1' WHEN "01", '0' WHEN "10", '1' WHEN "11"; Sve moguće vrednosti selekcionog signala moraju biti pokrivene. Za tip std_logic to nisu samo ˝00˝, ˝01˝, ˝10˝, ˝11˝, već i ˝0X˝, ˝HL˝, … (sve ukupno 64). Arhitektura mikrosistema

Realizacija tabele istinitosti Kompaktnije zapisivanje Arhitektura mikrosistema

SELECTPrimer: Multiplekser ARCHITECTURE select_arch OF mux4u1 IS BEGIN WITH sel SELECT y <= a WHEN "00", -- "," umesto ";" b WHEN "01", c WHEN "10", d WHEN OTHERS; -- ne moze d WHEN "11" END select_arch; Arhitektura mikrosistema

SELECTPrimer: Dekoder ARCHITECTURE select_arch OF dek2u4 IS SIGNAL ed : STD_LOGIC_VECTOR(2 DOWNTO 0); BEGIN ed <= e & d; WITH ed SELECT y <= "1000" WHEN "100", "0100" WHEN "101", "0010" WHEN "110", "0001" WHEN "111", "0000" WHEN OTHERS; END select_arch; Arhitektura mikrosistema

SELECTPrimer: Koder ARCHITECTURE select_arch OF encoder IS BEGIN WITH x SELECT y <= "00" WHEN "0001", "01" WHEN "0010", "10" WHEN "0100", "11" WHEN OTHERS; END select_arch; WITH x SELECT y <= "00" WHEN "0001", "01" WHEN "0010", "10" WHEN "0100", "11" WHEN "1000", "--" WHEN OTHERS; Arhitektura mikrosistema

SELECTPrimer: Prioritetni koder ARCHITECTURE select_arch OF pencoder IS BEGIN WITH x SELECT y <="00" WHEN "0001", "01" WHEN "0010" | "0011"; "10" WHEN "0100" | "0101" | "0110" | "0111", "11" WHEN OTHERS; WITH x SELECT z <= '0' WHEN "0000", '1' WHEN OTHERS; END select_arch; Arhitektura mikrosistema

SELECTPrimer: ALU Arhitektura mikrosistema

Konceptualna implementacija naredbe SELECT WITH sel SELECT sig <= izraz_1 WHEN v1, izraz_2 WHEN v2, ... izraz_n WHEN vn; WITH sel SELECT sig <= izraz_1 WHEN v1, izraz_2 WHEN v2, izraz_3 WHEN OTHERS Arhitektura mikrosistema

Konceptualna implementacija naredbe SELECT - primer SIGNAL s: STD_LOGIC_VECTOR(1 DOWNTO 0); . . . WITH s SELECT x <= (a AND b) WHEN "11", (a OR b) WHEN "01" | "10", ’0’ WHEN OTHERS; . . . Arhitektura mikrosistema

Konceptualna implementacija naredbe SELECT - primer SIGNAL a,b,r: UNSIGNED(7 DOWNTO 0); SIGNAL s: STD_LOGIC_VECTOR(1 DOWNTO 0); . . . WITH s SELECT r <= a+1 WHEN "11", a-b-1 WHEN "10", a+b WHEN OTHERS; . . . Arhitektura mikrosistema

´Z´ LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY tri_state IS PORT (ena : IN STD_LOGIC; input : IN STD_LOGIC_VECTOR(7 DOWNTO 0); output : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END tri_state; ARCHITECTURE tri_state OF tri_state IS BEGIN output <= input WHEN (ena = '0') ELSE (OTHERS => 'Z'); END tri_state; Arhitektura mikrosistema

´Z´ - ograničenja u sintezi • Ne može se koristiti kao ulazna vrednost, niti se s ovom vrednošću može manipulisati na način kao sa logičkim vrednostima ´0´ i ´1´. • Sledeće dve naredbe se ne mogu sintetizovati: r <= ’Z’ AND a; g <= d - c WHEN a = ’Z’ ELSE d - b; Arhitektura mikrosistema

Bidirekcioni (ulazno/izlazni) port • Port koji se po potrebi može koristiti bilo kao ulaz bilo kao izlaz. ENTITY bi_port IS PORT(... bi : INOUT STD_LOGIC; ...); BEGIN ... bi <= sig_out WHEN dir = ’1’ ELSE ’Z’; sig_in <= bi; ... Princip: Za dir=´1´, bi je izlaz Za dir=´0´, bi je ulaz Smer: inout Arhitektura mikrosistema

Trostatička magistrala LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY mux IS PORT ( a,b,c,d : IN STD_LOGIC; sel: IN STD_LOGIC_VECTOR(1 DOWNTO 0); y : OUT STD_LOGIC); END mux; ARCHITECTURE tri_state OF mux IS BEGIN y <= a WHEN sel = "00" ELSE 'Z'; y <= b WHEN sel = "01" ELSE 'Z'; y <= c WHEN sel = "10" ELSE 'Z'; y <= d WHEN sel = "11" ELSE 'Z'; END tri_state; Arhitektura mikrosistema Magistrala

ROM • ROM (prema eng. Read-Only Memory) je memorija sa konstantnim sadržajem - memorijska komponenta koja može samo da se čita. Arhitektura mikrosistema

ROM LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.NUMERIC_STD.ALL; ENTITY ROM IS PORT (addr : IN STD_LOGIC_VECTOR(2 DOWNTO 0); data : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END ROM; ARCHITECTURE rom OF ROM IS TYPE mem_array IS ARRAY (0 TO 7) OF STD_LOGIC_VECTOR(7 DOWNTO 0); CONSTANT memory : mem_array := ("00000000“ "00000010", "00000100", "00001000", "00010000", "00100000", "01000000", "10000000"); BEGIN data <= memory(TO_INTEGER(UNSIGNED(addr))); END rom; Zato što indeks polja može biti samo integer Arhitektura mikrosistema

Optimizacija konkurentnog koda • Cilj: sa što manje hardverskih resursa realizovati željenu funkciju • Minimizacija broja aritmetičkih i relacionih operatora u kodu • Dve tehnike: • Deoba operatora i • Deoba funkcija Arhitektura mikrosistema

Deoba operatora • Kako smanjiti broj aritmetičkih operatora u kodu? • Preurediti kôd tako da se se isti operator može iskoristiti za obavljanje više različitih operacija. r <= a + b WHEN uslov ELS a + c; x <= b WHEN uslov ELSE c; r <= a + x; Arhitektura mikrosistema

Složenost vs. kašnjenje Složenost: 2 sabirača + multiplekser Složenost: 1 sabirač + multiplekser Kašnjenje: max{Tsab, Tuslov} + Tmux Kašnjenje: Tsab + Tuslov + Tmux Arhitektura mikrosistema

Deoba operatora na primeru naredbe select: WITH uslov SELECT r <= a+b WHEN ˝00˝, a+c WHEN ˝01˝, d+1 WHEN OTHERS; WITH uslov SELECT x0 <= a WHEN ˝00˝ | ˝01˝, d WHEN OTHERS; WITH uslov SELECT x1 <= b WHEN ˝00˝, c WHEN ˝01˝, ˝00000001˝ WHEN OTHERS; r <= x0 + x1; Nivo ostvarene uštede zavisi od relativnog odnosa složenosti operatora i dodatnih multipleksera Arhitektura mikrosistema

Deoba funkcija • Više funkcija realizuju se tako da dele neke zajedničke delove ili se jedna funkcija koristi za realizaciju neke druge funkcije. Sabirač/oduzimač ARCHITECTURE arch_v1 OF ADDSUB IS SIGNAL x0, x1, sum : SIGNED(7 DOWNTO 0); BEGIN x0 <= SIGNED(a); x1 <= SIGNED(b); sum <= x0 + x1 WHEN ctrl = ‘0’ ELSE x0 - x1; r <= STD_LOGIC_VECTOR(sum); END arch_v1; Funkcionalna tabela Arhitektura mikrosistema

Deoba funkcija – optimizovana realizacija sabirača/oduzimača Oduzimanje je isto što i sabiranje s potpunim komplementom umanjioca: a - b = a + b’+ 1 ARCHITECTURE arch_v2 OF ADDSUB IS SIGNAL x0, x1, sum : UNSIGNED(7 DOWNTO 0); SIGNAL cin : UNSIGNED(0 DOWNTO 0); BEGIN x0 <= UNSIGNED(a); x1 <= UNSIGNED(b) WHEN ctrl=´0´ ELSE UNSIGNED(NOT b); cin <= ˝0˝ WHEN ctrl=´0´ ELSE ˝1˝; sum <= x0 + x1 + cin; r <= STD_LOGIC_VECTOR(sum); END arch_v2; ˝multiplekser + niz invertora˝ < ˝oduzimač˝ Arhitektura mikrosistema

Deoba funkcija na primeru komparatora Komparator (potpuni komparator) gt <= '1' WHEN a > b ELSE '0'; lt <= '1' WHEN a < b ELSE '0'; eq <= '1' WHEN a = b ELSE '0'; a> b a< b a= b Arhitektura mikrosistema

Deoba funkcija na primeru komparatora a je jednako b, ako a nije ni veće ni manje od b xgt <= '1' WHEN a > b ELSE '0'; xlt <= '1' WHEN a < b ELSE '0'; gt <= xgt; lt <= xlt; eq <= xgt NOR xlt; Još efikasnije: Arhitektura mikrosistema

Konkurentni kod - Ispitni zadatak Arhitektura mikrosistema

Konkurentni kod - Ispitni zadatakRešenje Arhitektura mikrosistema

Konkurentni kod - Ispitni zadatak Arhitektura mikrosistema

Konkurentni kod - Ispitni zadatakRešenje Zašto je neophodan pomoćni signal mux_out ? Arhitektura mikrosistema