delay-fault testing tutorial

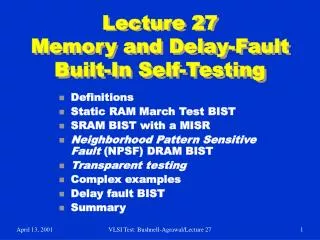

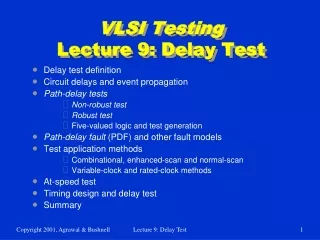

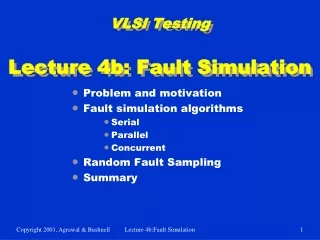

Delay Fault Testing Tutorial. 2. Outline. Common Fault Models (Review)Defects and Delay FaultsDelay Fault ModelsTransition FaultsPath Delay FaultsRobust Path TestNon-robust Path Test. Delay Fault Testing Tutorial. 3. Common Fault Models. Delay Fault Testing Tutorial. 4. Delay Fault Testing Tutorial.

delay-fault testing tutorial

E N D

Presentation Transcript

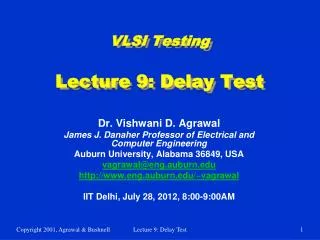

1. Delay-Fault Testing Tutorial Acknowledgement: This presentation is adapted from Professor Janak Patel�s tutorial on the same topic available on the web at: http://courses.ece.uiuc.edu/ece543/docs/DelayFault_6_per_page.pdf

2. Delay Fault Testing Tutorial 2

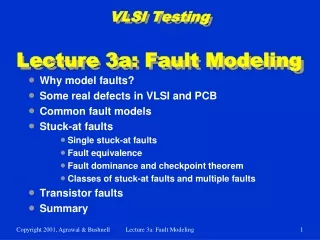

3. Delay Fault Testing Tutorial 3 Common Fault Models Here we shown some of the commonly used fault models that have appeared in the literature. The first two apply to the gate level and the third one to transistor-level models. The coupling and pattern interference faults have been considered thus far for memory circuits which are modeled at a functional level. However, these faults may receive more attention for logic testing as well as the dimensions of the devices shrink further.Here we shown some of the commonly used fault models that have appeared in the literature. The first two apply to the gate level and the third one to transistor-level models. The coupling and pattern interference faults have been considered thus far for memory circuits which are modeled at a functional level. However, these faults may receive more attention for logic testing as well as the dimensions of the devices shrink further.

4. Delay Fault Testing Tutorial 4

5. Delay Fault Testing Tutorial 5

6. Delay Fault Testing Tutorial 6

7. Delay Fault Testing Tutorial 7

8. Delay Fault Testing Tutorial 8

9. Delay Fault Testing Tutorial 9

10. Delay Fault Testing Tutorial 10

11. Delay Fault Testing Tutorial 11

12. Delay Fault Testing Tutorial 12

13. Delay Fault Testing Tutorial 13

14. Delay Fault Testing Tutorial 14

15. Delay Fault Testing Tutorial 15

16. Delay Fault Testing Tutorial 16

17. Delay Fault Testing Tutorial 17

18. Delay Fault Testing Tutorial 18

19. Delay Fault Testing Tutorial 19

20. Delay Fault Testing Tutorial 20

21. Delay Fault Testing Tutorial 21

22. Delay Fault Testing Tutorial 22

23. Delay Fault Testing Tutorial 23 Exercise Consider the 4-Nand implementation of the XOR gate in the previous slide. There are six I/O paths hence 12 path delay faults. For each of these faults, determine if it is robustly testable, only non-robustly testable or not testable (functionally redundant). Provide justification for your answers.

24. Delay Fault Testing Tutorial 24

25. Delay Fault Testing Tutorial 25

26. Delay Fault Testing Tutorial 26

27. Delay Fault Testing Tutorial 27

28. Delay Fault Testing Tutorial 28

29. Delay Fault Testing Tutorial 29 Timing for launch-off-capture Transition-delay fault testing

30. Delay Fault Testing Tutorial 30

31. Delay Fault Testing Tutorial 31 Timing for launch-off-shift Transition-delay fault testing

32. Delay Fault Testing Tutorial 32

33. Delay Fault Testing Tutorial 33

34. Delay Fault Testing Tutorial 34

35. Delay Fault Testing Tutorial 35

36. Delay Fault Testing Tutorial 36