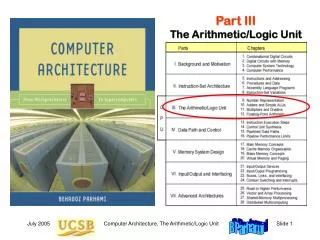

Part III The Arithmetic/Logic Unit

Part III The Arithmetic/Logic Unit. III The Arithmetic/Logic Unit. Overview of computer arithmetic and ALU design: Review representation methods for signed integers Discuss algorithms & hardware for arithmetic ops Consider floating-point representation & arithmetic.

Part III The Arithmetic/Logic Unit

E N D

Presentation Transcript

Part IIIThe Arithmetic/Logic Unit Computer Architecture, The Arithmetic/Logic Unit

III The Arithmetic/Logic Unit • Overview of computer arithmetic and ALU design: • Review representation methods for signed integers • Discuss algorithms & hardware for arithmetic ops • Consider floating-point representation & arithmetic Computer Architecture, The Arithmetic/Logic Unit

11 Multipliers and Dividers • Modern processors perform many multiplications & divisions: • Encryption, image compression, graphic rendering • Hardware, vs programmed shift-add/sub, algorithms Computer Architecture, The Arithmetic/Logic Unit

11.1 Shift-Add Multiplication Figure 11.1 Multiplication of 4-bit numbers in dot notation. z(j+1) = (z(j) + yjx 2k) 2–1 with z(0) = 0 and z(k) = z |––– add –––| |–– shift right ––| Computer Architecture, The Arithmetic/Logic Unit

Example 11.1 Binary and Decimal Multiplication Position 7 6 5 4 3 2 1 0 Position 7 6 5 4 3 2 1 0 ========================= ========================= x24 1 0 1 0 x104 3 5 2 8 y 0 0 1 1 y 4 0 6 7 ========================= ========================= z(0) 0 0 0 0 z(0) 0 0 0 0 +y0x24 1 0 1 0 +y0x104 2 4 6 9 6 –––––––––––––––––––––––––– –––––––––––––––––––––––––– 2z(1) 0 1 0 1 0 10z(1) 2 4 6 9 6 z(1) 0 1 0 1 0 z(1) 0 2 4 6 9 6 +y1x24 1 0 1 0 +y1x104 2 1 1 6 8 –––––––––––––––––––––––––– –––––––––––––––––––––––––– 2z(2) 0 1 1 1 1 0 10z(2) 2 3 6 3 7 6 z(2) 0 1 1 1 1 0 z(2) 2 3 6 3 7 6 +y2x24 0 0 0 0 +y2x104 0 0 0 0 0 –––––––––––––––––––––––––– –––––––––––––––––––––––––– 2z(3) 0 0 1 1 1 1 0 10z(3) 0 2 3 6 3 7 6 z(3) 0 0 1 1 1 1 0 z(3) 0 2 3 6 3 7 6 +y3x24 0 0 0 0 +y3x104 1 4 1 1 2 –––––––––––––––––––––––––– –––––––––––––––––––––––––– 2z(4) 0 0 0 1 1 1 1 0 10z(4) 1 4 3 4 8 3 7 6 z(4) 0 0 0 1 1 1 1 0 z(4) 1 4 3 4 8 3 7 6 ========================= ========================= Figure 11.2 Step-by-step multiplication examples for 4-digit unsigned numbers. Computer Architecture, The Arithmetic/Logic Unit

Example 11.2 Two’s-Complement Multiplication Position 7 6 5 4 3 2 1 0 Position 7 6 5 4 3 2 1 0 ========================= ========================= x24 1 0 1 0 x24 1 0 1 0 y 0 0 1 1 y 1 0 1 1 ========================= ========================= z(0) 0 0 0 0 0 z(0) 0 0 0 0 0 +y0x24 1 1 0 1 0 +y0x24 1 1 0 1 0 –––––––––––––––––––––––––– –––––––––––––––––––––––––– 2z(1) 1 1 0 1 0 2z(1) 1 1 0 1 0 z(1) 1 1 1 0 1 0 z(1) 1 1 1 0 1 0 +y1x24 1 1 0 1 0 +y1x24 1 1 0 1 0 –––––––––––––––––––––––––– –––––––––––––––––––––––––– 2z(2) 1 0 1 1 1 0 2z(2) 1 0 1 1 1 0 z(2) 1 1 0 1 1 1 0 z(2) 1 1 0 1 1 1 0 +y2x24 0 0 0 0 0 +y2x24 0 0 0 0 0 –––––––––––––––––––––––––– –––––––––––––––––––––––––– 2z(3) 1 1 0 1 1 1 0 2z(3) 1 1 0 1 1 1 0 z(3) 1 1 1 0 1 1 1 0 z(3) 1 1 1 0 1 1 1 0 +(–y3x24) 0 0 0 0 0 +(–y3x24) 0 0 1 1 0 –––––––––––––––––––––––––– –––––––––––––––––––––––––– 2z(4) 1 1 1 0 1 1 1 0 2z(4) 0 0 0 1 1 1 1 0 z(4) 1 1 1 0 1 1 1 0 z(4) 0 0 0 1 1 1 1 0 ========================= ========================= Figure 11.3 Step-by-step multiplication examples for 2’s-complement numbers. Computer Architecture, The Arithmetic/Logic Unit

11.2 Hardware Multipliers Figure 11.4 Hardware multiplier based on the shift-add algorithm. Computer Architecture, The Arithmetic/Logic Unit

The Shift Part of Shift-Add Figure11.5 Shifting incorporated in the connections to the partial product register rather than as a separate phase. Computer Architecture, The Arithmetic/Logic Unit

High-Radix Multipliers Radix-4 multiplication in dot notation. z(j+1) = (z(j) + yjx 2k) 4–1 with z(0) = 0 and z(k/2) = z |––– add –––| |–– shift right ––| Assume k even Computer Architecture, The Arithmetic/Logic Unit

Tree Multipliers Figure 11.6 Schematic diagram for full/partial-tree multipliers. Computer Architecture, The Arithmetic/Logic Unit

Array Multipliers Figure 11.7 Array multiplier for 4-bit unsigned operands. Computer Architecture, The Arithmetic/Logic Unit

11.3 Programmed Multiplication MiniMIPS instructions related to multiplication mult $s0,$s1 # set Hi,Lo to ($s0)($s1); signed multu $s2,$s3 # set Hi,Lo to ($s2)($s3); unsigned mfhi $t0 # set $t0 to (Hi) mflo $t1 # set $t1 to (Lo) Example 11.3 Finding the 32-bit product of 32-bit integers in MiniMIPS Multiply; result will be obtained in Hi,Lo For unsigned multiplication: Hi should be all-0s and Lo holds the 32-bit result For signed multiplication: Hi should be all-0s or all-1s, depending on the sign bit of Lo Computer Architecture, The Arithmetic/Logic Unit

Multiplication When There Is No Multiply Instruction Example 11.4 (MiniMIPS shift-add program for multiplication) Figure 11.8 Register usage for programmed multiplication superimposed on the block diagram for a hardware multiplier. Computer Architecture, The Arithmetic/Logic Unit

MIPS Assembly Code forthis Multiplication Algorithm shamu: move $v0,$zero # Initialize Hi to 0 move $v1,$zero # Initialize Lo to 0 addi $t2,$zero,32 # Initialize repetition counter to 32. mloop: move $t0,$zero # Loop: Initialize carry to 0. andi $t1,$a1,1 # LSB of multiplier to shift out. srl $a1,$a1,1 # Shift the multiplier right. beqz $t1,no_add # If bit shifted out was not 0, then addu $v0,$v0,$a0 # add multiplicand into Hi word, sltu $t0,$v0,$a0 # and remember the carry out. no_add: andi $t1,$v0,1 # LSB of Hi word to shift out. srl $v0,$v0,1 # Shift Hi word of product right. sll $t0,$t0,31 # Shift carry left to position 31. or $v0,$t0,$v0 # OR the carry into the Hi word. srl $v1,$v1,1 # Shift Lo word of product right. sll $t1,$t1,31 # Shift bit left to position 31. or $v1,$t1,$v1 # OR the bit into the Lo word. addi $t2,$t2,-1 # Decrement loop counter. bnez $t2,mloop # Continue while counter is nonzero. jr $ra # Return product=($v0,$v1) to caller. Michael Frank, FAMU-FSU College of Engineering

C language equivalent unsignedlong shamu(unsignedintmcand, unsignedintmer) { unsignedintHi,Lo,carry,bit,counter; Lo = Hi = 0; /* Initialize product registers to 0. */ counter = 32; /* Initialize repetition counter to 32. */ do { /* Repeat the following loop: */ carry = 0; /* Initialize carry-out bit to 0. */ bit = mer & 1; /* t1 := LSB of m'er. */ mer >>= 1; /* Shift m'er right by 1. */ if (bit) { /* If low bit of multiplier was 1, then */ Hi += mcand; /* Add mcand into Hi */ carry = (Hi < mcand); /* Carry out from add */ } /* END IF. */ bit = Hi & 1; /* LSB of Hi */ Hi = (carry << 31) & (Hi >> 1); /* Shift carry into Hi */ Lo = (bit << 31) & (Lo >> 1); /* Shift into Lo */ counter--; /* Decrement counter. */ } while (counter > 0); return ((unsignedlong)Hi)<<32 & Lo; /* Return 64-bit result. */ } /* END FUNCTION shamu() */ Michael Frank, FAMU-FSU College of Engineering

11.4 Shift-Subtract Division Figure11.9 Division of an 8-bit number by a 4-bit number in dot notation. z(j) = 2z(j-1)-yk-jx 2k with z(0) = z and z(k) = 2ks |shift| |–– subtract ––| Computer Architecture, The Arithmetic/Logic Unit

Example 11.5 Integer and Fractional Unsigned Division Position 7 6 5 4 3 2 1 0 Position –1 –2 –3 –4 –5 –6 –7 –8 ========================= ========================== z 0 1 1 1 0 1 0 1 z. 1 4 3 5 1 5 0 2 x24 1 0 1 0 x. 4 0 6 7 ========================= ========================== z(0) 0 1 1 1 0 1 0 1 z(0). 1 4 3 5 1 5 0 2 2z(0) 0 1 1 1 0 1 0 1 10z(0) 1 . 4 3 5 1 5 0 2 –y3x24 1 0 1 0 y3=1 –y–1x 1 . 2 2 0 1 y–1=3 –––––––––––––––––––––––––– ––––––––––––––––––––––––––– z(1) 0 1 0 0 1 0 1 z(1). 2 1 5 0 5 0 2 2z(1) 0 1 0 0 1 0 1 10z(1) 2 . 1 5 0 5 0 2 –y2x24 0 0 0 0 y2=0 –y–2x 2 . 0 3 3 5 y–2=5 –––––––––––––––––––––––––– ––––––––––––––––––––––––––– z(2) 1 0 0 1 0 1 z(2). 1 1 7 0 0 2 2z(2) 1 0 0 1 0 1 10z(2) 1 . 1 7 0 0 2 –y1x24 1 0 1 0 y1=1 –y–3x 0 . 8 1 3 4 y–3=2 –––––––––––––––––––––––––– ––––––––––––––––––––––––––– z(3) 1 0 0 0 1 z(3). 3 5 6 6 2 2z(3) 1 0 0 0 1 10z(3) 3 . 5 6 6 2 –y0x24 1 0 1 0 y0=1 –y–4x 3 . 2 5 3 6 y–4=8 –––––––––––––––––––––––––– ––––––––––––––––––––––––––– z(4) 0 1 1 1 z(4). 3 1 2 6 s 0 1 1 1 s. 0 0 0 0 3 1 2 6 y 1 0 1 1 y. 3 5 2 8 ========================= ========================== Figure 11.10 Division examples for binary integers and decimal fractions. Computer Architecture, The Arithmetic/Logic Unit

Example 11.6 Division with Same-Width Operands Position 7 6 5 4 3 2 1 0 Position –1 –2 –3 –4 –5 –6 –7 –8 ========================= ========================== z 0 0 0 0 1 1 0 1 z. 0 1 0 1 x24 0 1 0 1 x. 1 1 0 1 ========================= ========================== z(0) 0 0 0 0 1 1 0 1 z(0). 0 1 0 1 2z(0) 0 0 0 1 1 0 1 2z(0) 0 . 1 0 1 0 –y3x24 0 0 0 0 y3=0 –y–1x 0 . 0 0 0 0 y–1=0 –––––––––––––––––––––––––– ––––––––––––––––––––––––––– z(1) 0 0 0 1 1 0 1 z(1). 1 0 1 0 2z(1) 0 0 1 1 0 1 2z(1) 1 . 0 1 0 0 –y2x24 0 0 0 0 y2=0 –y–2x 0 . 1 1 0 1 y–2=1 –––––––––––––––––––––––––– ––––––––––––––––––––––––––– z(2) 0 0 1 1 0 1 z(2). 0 1 1 1 2z(2) 0 1 1 0 1 2z(2) 0 . 1 1 1 0 –y1x24 0 1 0 1 y1=1 –y–3x 0 . 1 1 0 1 y–3=1 –––––––––––––––––––––––––– ––––––––––––––––––––––––––– z(3) 0 0 0 1 1 z(3). 0 0 0 1 2z(3) 0 0 1 1 2z(3) 0 . 0 0 1 0 –y0x24 1 0 1 0 y0=0 –y–4x 0 . 0 0 0 0 y–4=0 –––––––––––––––––––––––––– ––––––––––––––––––––––––––– z(4) 0 0 1 1 z(4). 0 0 1 0 s 0 0 1 1 s. 0 0 0 0 0 0 1 0 y 0 0 1 0 y. 0 1 1 0 ========================= ========================== Figure 11.11 Division examples for 4/4-digit binary integers and fractions. Computer Architecture, The Arithmetic/Logic Unit

C++ function for division of unsigned 32-bit integers unsignedint myDivide // DEFINE FUNCTION myDivide(): (unsignedintdividend, // Argument 0: Number to be divided. unsignedintdivisor, // Argument 1: Number to divide it by. unsignedint &remainder) // Argument 2: Place to put remainder. {unsignedintquotient = 0; // Quotient: Initially zero. intposition = 0; // Bit position: Initially zero. while (!(divisor & (1<<31))) {// While divisor MSB is empty, position++; // Increment bit position, divisor <<= 1; } // & shift divisor left. do{quotient <<= 1; // Repeatedly, make room for quotient bit; if (dividend >= divisor) { // if we can do a subtraction here, dividend -= divisor; // then do it, quotient |= 1; } // and set quotient bit to 1; divisor >>= 1; } // shift divisor right to a new position; while (--position >= 0); // decrement pos and continue while >=0 remainder = dividend; // Remainder is the remaining dividend. returnquotient;} // Return quotient (& remainder). Michael Frank, FAMU-FSU College of Engineering

Equivalent MIPS assembly for 32-bit unsigned division myDivide: move $v0, $zero # quotient := 0; move $t0, $zero # position := 0; leftShift: and $t1, $a1, 0x80000000 # while (divisor & 0x80000000 bne $t1, $zero, doTop # != 0) { addi $t0, $t0, 1 # position++; sll $a1, $a1, 1 # divisor <<= 1; b leftShift # } doTop: sll $v0, $v0, 1 # do { quotient <<= 1; sltu $t1, $a0, $a1 # $t4 := (dividend < divisor) bne $t1, $zero, endIf # if ($t4 == 0) {// d’dend >= d’sor subu $a0, $a0, $a1 # dividend -= divisor; or $v0, $v0, 1 # quotient |= 1; } endIf: srl $a1, $a1, 1 # divisor >>= 1; addi $t0, $t0, -1 # position--; bgez $t0, doTop # } while (position >= 0); endFor: sw $a0, 0($a2) # rem := remainder; jr $ra # return. Michael Frank, FAMU-FSU College of Engineering

Signed Division Method 1 (indirect): strip operand signs, divide, set result signs DividendDivisorQuotientRemainder z = 5 x = 3 y = 1 s = 2 z = 5 x = –3 y = –1 s = 2 z = –5 x = 3 y = –1 s = –2 z = –5 x = –3 y = 1 s = –2 Method 2 (direct 2’s complement): develop quotient with digits –1 and 1, chosen based on signs, convert to digits 0 and 1 Restoring division: perform trial subtraction, choose 0 for q digit if partial remainder negative Nonrestoring division: if sign of partial remainder is correct, then subtract (choose 1 for q digit) else add (choose –1) Computer Architecture, The Arithmetic/Logic Unit

11.5 Hardware Dividers Figure 11.12 Hardware divider based on the shift-subtract algorithm. Computer Architecture, The Arithmetic/Logic Unit

The Shift Part of Shift-Subtract Figure 11.13 Shifting incorporated in the connections to the partial remainder register rather than as a separate phase. Computer Architecture, The Arithmetic/Logic Unit

High-Radix Dividers Radix-4 division in dot notation. z(j) = 4z(j-1)- (yk-2j+1yk-2j)twox 2k with z(0) = z and z(k/2) = 2ks |shift| |––––––– subtract –––––––| Assume k even Computer Architecture, The Arithmetic/Logic Unit

Array Dividers Figure 11.14 Array divider for 8/4-bit unsigned integers. Computer Architecture, The Arithmetic/Logic Unit

11.6 Programmed Division MiniMIPS instructions related to division div $s0,$s1 # Lo = quotient, Hi = remainder divu $s2,$s3 # unsigned version of division mfhi $t0 # set $t0 to (Hi) mflo $t1 # set $t1 to (Lo) Example 11.7 Compute z mod x, where z (singed) and x > 0 are integers Divide; remainder will be obtained in Hi if remainder is negative, then add |x| to (Hi) to obtain z mod x else Hi holds z mod x Computer Architecture, The Arithmetic/Logic Unit

Division via Repeated Subtractions Example 11.8 (MiniMIPS shift-add program for division) Figure 11.15 Register usage for programmed division superimposed on the block diagram for a hardware divider. Computer Architecture, The Arithmetic/Logic Unit

Divider vs Multiplier: Hardware Similarities Figure 11.12 Figure 11.4 Turn upside-down Figure 11.14 Figure 11.7 Computer Architecture, The Arithmetic/Logic Unit