Module Protection chip “MPC” for Serial Powered Pixel Module

60 likes | 82 Vues

This module protection chip (MPC) by Laura Gonella, Hans Krüger, and Andreas Eyring of Bonn University is designed for serial powered pixel modules. It ensures efficient power distribution at CERN and features fast auto-response, low power dissipation, and radiation tolerance. The chip enables easy control and monitoring while meeting SCR MPC requirements. It includes OV protection, voltage monitoring, and reset functionality. Future steps involve defining MOSFET type and diode behavior for optimal performance.

Module Protection chip “MPC” for Serial Powered Pixel Module

E N D

Presentation Transcript

Module Protection chip “MPC” for Serial Powered Pixel Module Laura Gonella, Hans Krüger, Andreas Eyring Bonn University Andreas Eyring, Power Distribution, Cern 24.02.2009

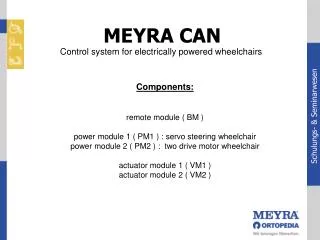

SCR Serial powering sceme MPC = on I in = 3,6 A DCS on EOSC I = 0,8 * 4 chips = 3,6 A local VDD D1 MPC1 4chipsmodule D2 + simple + control & monitor + fast auto-response default state = OC - 1 AWG 36 line / module I out = 3.6 A R D3 4chipsmodule MPC2 local GND 4chipsmodule MPCx OC = Open Circuit (ie switch is “off”, module powered) 15

SCR MPC requirements • AC or DC controlled BTrequirement: low power dissipation Ron = very low • OV protection with SCRrequirement: low power dissipation Ron = very low; self - acting • Module voltage monitoring over the control line • Radiation tolerant for 100 Mrad for outer pixel layers DCS on EOS Card I in = 3,6 A from previous module MPC ADC BT module C1 Zener diode could be nessesary for DC control GND I out = 3.6 A to next module Andreas Eyring, Power Distribution, Cern 24.02.2009

MPC specification Note: Reset of the SCR possible via the control line by on/off swtching the BT! Andreas Eyring, Power Distribution, Cern 24.02.2009

Next steps • define the MOSFET type and dimension for 3.6A • define the diode behavior ( very low voltage drop) • do detailed simulations & design the chip • radiation hardness has to be tested • first prototype by summer/fall 2009 Andreas Eyring, Power Distribution, Cern 24.02.2009

SCR simulation 130 nm IBM CMOS SCR: Q2 begins to conductQ1 switches on Q2 draws even more current IT1 Q1 Q2 Iload Uthr Q1 Sweep of Rload Q2 VDD Uthr Vdd=Uthr * (2+R2/R1) Andreas Eyring, Power Distribution, Cern 24.02.2009