Comprehensive Guide to Accessing DSP GPIO Pins and CPLD Programming

This guide covers essential details on accessing DSP GPIO pins, address bus, control bus, and data bus connections. It includes header definitions and jumper configurations for various power options, including external power, XDS-100 USB, and DSP UART USB. Additionally, it provides insights on integrating the Altera EPM3064ALC44 CPLD, including JTAG programming details and specific pin access for the Analog to Digital Converter (ADC). Perfect for engineers looking to harness the full capabilities of DSP and CPLD systems.

Comprehensive Guide to Accessing DSP GPIO Pins and CPLD Programming

E N D

Presentation Transcript

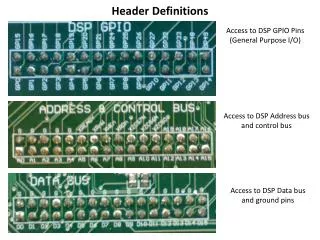

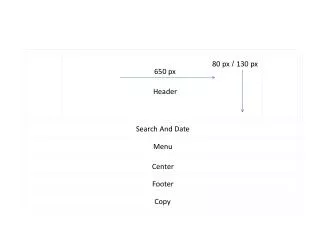

Access to DSP GPIO Pins (General Purpose I/O) Header Definitions Access to DSP Address bus and controlbus Access to DSP Data bus and ground pins

Header Definitions (continued) CPLD JTAG for programmingan Altera EPM3064ALC44-10CPLD if populated Access to DSP Analog to Digital Converter (ADC) Access to CPLD pins (actual EPM3064ALC44 pin number)

Jumper Definitions This position used when powering using Ext Pwr (+5V) Header This position used when powering from XDS-100 USB This position used when powering from DSP UART USB Jumpersbetween DSP signals and hardwired CPLD pins