MultiNoC

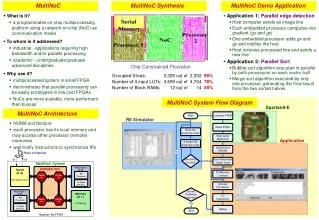

MultiNoC. MultiNoC Synthesis. MultiNoC Demo Application. Application 1: Parallel edge detection Host computer sends an image line Each embedded processor computes one gradient ( gx and gy ) One embedded processor adds gx and gy and notifies the host

MultiNoC

E N D

Presentation Transcript

MultiNoC MultiNoC Synthesis MultiNoC Demo Application • Application 1:Parallel edge detection • Host computer sends an image line • Each embedded processor computes one gradient (gx and gy) • One embedded processor adds gx and gy and notifies the host • Host receives processed line and sends a new line • Application 2:Parallel Sort • Bubble sort algorithm executed in parallel by both processors on each vector half • Merge sort algorithm executed by only one processor, generating the final result from the two sorted halves. • What is it? • a programmable on-chip multiprocessing platform using a network-on-chip (NoC) as communication media • To whom is it addressed? • industrial - applications requiring high bandwidth and/or parallel processing • academic - undergraduate/graduate advanced disciplines • Why use it? • multiprocessed system in small FPGA • demonstrates that parallel processing can be easily prototyped in low cost FPGAs • NoCs are more scalable, more performant than busses Chip Constrained Floorplan Occupied Slices: Number of 4 input LUTs: Number of Block RAMs: 2,325 out of 2,352 98% 3,699 out of 4,704 78% 12 out of 14 85% MultiNoC System Flow Diagram SpartanII-E MultiNoC Architecture R8 Simulator • NUMA architecture • each processor has its local memory and may access other processor (remote) memories • wait/notify instructions to synchronize IPs Application

Interconnection Structures Dedicated Wires Shared Bus Network-on-Chip (NoC) Parallelism + + - + + Power Consumption Lower, shorter wires Higher,longer wires Lower, shorter wires Scalability - - + + + Reusability - + + + + NoC – Network on a Chip CONTACT Leandro Möller, Graduate Computer Science Student Aline Mello, Graduate Computer Science Student Everton Carara, Undergraduate Computer Science Student Fernando Moraes, Professor Ney Calazans, Professor {moller, alinev, carara, moraes, calazans}@inf.pucrs.br SOME HERMES REFERENCES Moraes, F.; Mello, A; Möller, L; Ost, L.; Calazans, N.A Low Area Overhead Packet-switched Network on Chip: Architecture and Prototyping.In: IFIP VLSI SOC 2003, pp. 318-323. Moraes, F.; Calazans, N.; Mello, A.; Möller, L.; Ost, L.HERMES: an Infrastructure for Low Area Overhead Packet-switching Networks on Chip.Integration, the VLSI Journal, IN PRESS, 2004. ADDRESS Faculdade de Informática - PUCRSAv. Ipiranga, 6681 - Prédio 16 90619-900 - PORTO ALEGRE - BRASIL Telefone: +55 51 3320 3611FAX: +55 51 3320 3621http://www.inf. pucrs.br/~gaph Grupo de Apoio ao Projeto de Hardware Hardware Design Support Group MultiNoC PUCRS MultiNoC IPs • HERMES IP • 2 x 2 mesh network • wormhole packet switching • no global address map - NUMA • 8 different message formats: read memory, write memory, active processor, printf, scanf, scanf return, printf return, notify • R8 embedded processor IP • load-store 16-bit processor architecture • 16x16 bit register file • 36 distinct instructions • 1K 16-bit words local memory for program and data • Memory IP • 1K 16-bit words, using 4 Block RAMs • Serial IP • RS-232 protocol • provides bidirectional communication with a host processor A Multiprocessing System Enabled by a Network on Chip Xilinx Design Contest SBCCI 04