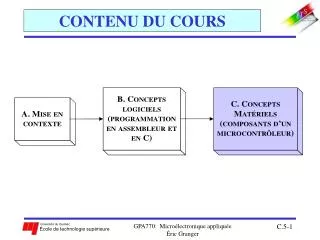

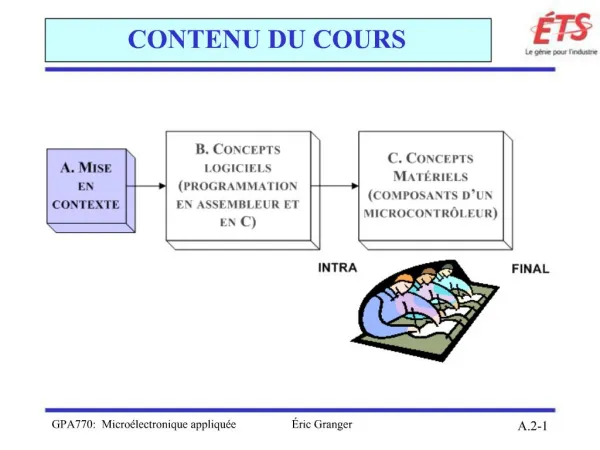

CONTENU DU COURS

950 likes | 1.08k Vues

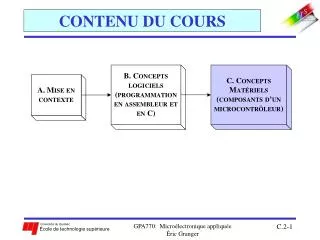

CONTENU DU COURS. Partie C − Concepts matériels. C.1 Con figurations matérielles du 68HC12: architecture du système, mémoire, et ports d’e/s C.2 Gestion d’exceptions: réponses aux remises-à-zéro et aux interruptions avec le 68HC12

CONTENU DU COURS

E N D

Presentation Transcript

CONTENU DU COURS GPA770: Microélectronique appliquée Éric Granger

Partie C − Concepts matériels C.1 Configurations matérielles du 68HC12: • architecture du système, mémoire, et ports d’e/s C.2 Gestion d’exceptions: • réponses aux remises-à-zéro et aux interruptions avec le 68HC12 • vecteur et priorité d’exceptions, et routines de service d’interruption C.3 Module de temporisation: • module de temporisation standard du 68HC12 • saisie des entrées et comparaison de sorties C.4 Convertisseurs analogique-numérique: • processus de conversion • système de conversion du 68HC12 C.5Interfaces de communications sérielles: • Communications sérielles avec un microcontrôleur • interfaces multiples du 68HCS12: SCI et SPI GPA770: Microélectronique appliquée Éric Granger

Sommaire de la section C.5 C.5 Interfaces sériels de communication du 68HC12: • Communications sérielles avec microcontrôleurs 2) Sous-systèmes multiples du 68HCS12 • Interface sériel asynchrone – SCI: • caractéristiques du sous-système SCI • registres, programmation et applications • Interface sériel synchrone – SPI: • caractéristiques du sous-système SPI • registres, programmation et applications GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (a) Communications avec un microcontrôleur • applications indépendantes à distance: • pour échanger des informations avec un composant distant • ex: communications entre deux robots mobiles • applications locales spécialisées dans un système: • pour interfacer directement avec un composant externes, et donc étendre les capacités • ex: communications avec l’afficheur LCD du robot mobile GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (b) Transmission parallèle vs sérielle • parallèle: mécanisme permettant le transfert de plusieurs bits à la fois entre 2 composants • transfert plus rapide de données • requiert 9-10 fils pour gérer un canal de 8 bits • consomme plus de broches d’e/s et de matériel GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (b) Transmission parallèle vs sérielle • sérielle: mécanisme permettant le transfert d’un bit à la fois entre 2 composants • transfert moins rapide de données • requiert 1-2 fils pour un canal de 1 bit • consomme peu de broches d’e/s et de matériel GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (b) Transmission parallèle vs sérielle • Transfert parallèle de données entre 68HC12: • peut connecter le Port A du transmetteur (configuré en sortie) au Port A du récepteur (configuré en entrée) pour transférer 8 bits • peut aussi connecter le Port B pour transférer 16 bits GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (b) Transmission parallèle vs sérielle • Communication à 8 bits entre deux 68HC12: • le 68HCS12 transmetteur écrit les données sur le port A, un octet à la fois • le 68HCS12 récepteur lit les données sur le port A, un octet à la fois • Exemple: transmission de 5 octets correspondant aux 5 caractères ASCII ‘hello’ GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (b) Transmission parallèle vs sérielle • Synchronisation: permet d’indiquer au récepteur quand les données transmises sont valides • Deux techniques de transfert: • parallèle synchrone: exploite un fil supplémentaire pour transporter un signal d’horloge commun entre transmetteur et récepteur • parallèle asynchrone: exploite deux fils supplémentaires pour réaliser du ‘handshaking’ entre transmetteur et récepteur GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (b) Transmission parallèle vs sérielle • Approche 1 – transmission synchrone: utiliser 1 fil supplémentaire pour transporter un signal d’horloge GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (b) Transmission parallèle vs sérielle • Communication à 8 bits entre deux 68HCS12: • le 68HC12 récepteur lit les données au port A sur le front montant du signal d’horloge • Exemple: transmission de 5 octets correspondant aux 5 caractères ASCII ‘hello’ GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (b) Transmission parallèle vs sérielle • Approche 2 – transmission asynchrone: utiliser 2 fils supplémentaires pour réaliser du ‘handshaking’ GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (b) Transmission parallèle vs sérielle • Communication à 8 bits entre deux 68HCS12: • le 68HCS12 transmetteur utilise un fil ‘Data Valid’ (DV) pour indiquer que les données sont valides • le 68HCS12 récepteur utilise un fil ‘Data Received’ (DR) pour indiquer qu’il a lu l’octet au port A GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (b) Transmission parallèle vs sérielle • Étapes d’une transmission parallèle asynchrone: • le transmetteur écrit les données sur son port A, et fixe DV = ‘L’ pour indiquer la disponibilité d’un nouvel octet • quand le récepteur détecte la disponibilité d’un nouveau octet, il lit son port A, et fixe DR = ‘L’ pour confirmer • quand le transmetteur détecte DR = ‘L’, il fixe DV = ‘H’ • quand le récepteur détecte DV = ‘H’, il fixe DR = ‘H’ Les deux microcontrôleurs sont maintenant prêts pour la prochaine transmission de données... GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (b) Transmission parallèle vs sérielle • Communication de données entre deux 68HCS12: • une communication entre transmetteur et récepteur se fait un bit à la fois, à travers d’un seul fil GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (b) Transmission parallèle vs sérielle • Synchronisation: le transmetteur doit indiquer au récepteur quand les bits sont valides • Deux techniques de transfert: • sériel synchrone: exploite un fil supplémentaire pour transporter un signal d’horloge commun entre transmetteur et récepteur • sériel asynchrone: exploite des bits spéciaux pour indiquer le début et la fin d’une communication entre transmetteur et le récepteur GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (b) Transmission parallèle vs sérielle • Approche 1 – transmission sériel synchrone: GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (b) Transmission parallèle vs sérielle • Étapes d’une communication sériel synchrone: • place un caractère à transmettre dans un registre à décalage interne • décalages successifs de n bits selon l’horloge (clk): • le transmetteur décale les bits d’un registre interne vers sa broche de sortie selon clk • le récepteur décale les bits sur sa broche d’entrée vers un registre interne selon clk • après n cycles d’horloge, n bits sont communiqués du transmetteur au récepteur GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (b) Transmission parallèle vs sérielle • Approche 2 – transmission sériel asynchrone: GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (b) Transmission parallèle vs sérielle • Étapes d’une communication sériel asynchrone: • les deux 68HCS12 sont configurés avec les mêmes paramètres de transmission (fréquence clk, bits/caractère, parité, etc.) • les données sont transmises sur un canal TxD→ RxD: • le transmetteur transmet un bit de départ (détecté par le récepteur) pour indiquer le début du transfert • le transmetteur transmet un caractère, LSb en premier, (détecté par le récepteur) • le transmetteur transmet un bit de terminaison (détecté par le récepteur) pour indiquer le fin du transfert GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (c) Concepts fondamentaux et terminologie • Lien sériel de communications: canal simple de communication, avec les données transférées un bit à la fois • Horloge: signal de synchronisation qui établit le taux de transfert des données (en synchrone) • Taux de transfert (Baud): nombre de bits transmit par second en bps ≡ Baud • ex: 1200, 2400, 4800, 9600 Baud < GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (c) Concepts fondamentaux et terminologie • cellule binaire ou période de bit: période de temps réservé pour la transmission d’un bit dans une séquence binaire (1 ∕ taux de transfert) • code NRZ (‘Non-Return-to-Zero’): format commun pour le transfert d’une séquence binaire • règle: pour transmettre ‘0’ (‘1’), placer la tension L (H) sur le canal pour toute la cellule binaire. GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (c) Concepts fondamentaux et terminologie • code ASCII: ‘American Standard Code for Information and Interchange’ GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (c) Concepts fondamentaux et terminologie • bit de parité: mécanisme pour détecter une erreur simple de transmission • réalisation: bit additionnel (e.g., MSb) qui indique la parité d’une séquence de bits • parité paire: le bit de parité est fixé tel qu’il y a un nombre pair de bits = ‘1’ dans le code • parité impaire: le bit de parité est fixé tel qu’il y a un nombre impair de bits = ‘1’ dans le code GPA770: Microélectronique appliquée Éric Granger

C.5(1) Communications sérielles (c) Concepts fondamentaux et terminologie • Types de communications sérielles: • lien simplexe: transfert sur 1 fil dans une direction (e.g., radio, TV) • lien mi-duplexe: transfert sur 1 fil dans les deux directions, mais pas simultanément (e.g., CB, BDM) • lien duplexe: transfert sur 2 fils dans les deux direction simultanément GPA770: Microélectronique appliquée Éric Granger

Sommaire de la section C.5 C.5 Interfaces sériels de communication du 68HC12: • Communications sérielles avec microcontrôleurs 2) Sous-systèmes multiples du 68HCS12 • Interface sériel asynchrone – SCI: • caractéristiques du sous-système SCI • registres, programmation et applications • Interface sériel synchrone – SPI: • caractéristiques du sous-système SPI • registres, programmation et applications GPA770: Microélectronique appliquée Éric Granger

C.5(2) Sous-systèmes du 68HC12 • Rôle des types de sous-systèmes dans le 68HCS12: • CPU12:unité de traitement central • gestion d’exceptions: interrompre l’exécution normal d’un programme • Bus: module LIM combine DATA, ADDR et CTRL • Mémoire: stocker des configurations (bloc), des variables (RAM) et des programmes (ROM) • Périphériques d’entrée/sortie: • ports d’entrée/sortie: échanger des données avec le monde externe • temporisation: capter des entrées, générer des sorties, accumuler des impulsions, PWM • conversion de données: convertir un signal analogique en codes binaires non-signés • communication sérielle: échanger de données par communications asynchrones (SCI) et synchrones (SPI) GPA770: Microélectronique appliquée Éric Granger

C.5(2) Sous-systèmes du 68HC12 MC9S12C32 GPA770: Microélectronique appliquée Éric Granger

C.5(2) Sous-systèmes du 68HC12 TX/RX Port S GPA770: Microélectronique appliquée Éric Granger

C.5(2) Sous-systèmes du 68HC12 • Module d’horloge: le 68HCS12 utiliseXTAL (÷2) = Bus Clock • 16MHz ÷ 2 = 8MHz • Pour contrôler le SCI et le SPI GPA770: Microélectronique appliquée Éric Granger

C.5(2) Sous-systèmes du 68HC12 • Module SCI (‘Serial Communications Interface’): • interface sériel pour communications • types de communications: sérielles asynchrones • synchronisation: utilise un bit de début et un bit d’arrêt pour encadrer chaque caractère transmis • utilisation typique: communiquer des caractères ASCII de façon asynchrone, à travers 1 fil GPA770: Microélectronique appliquée Éric Granger

C.5(2) Sous-systèmes du 68HC12 GPA770: Microélectronique appliquée Éric Granger

C.5(2) Sous-systèmes du 68HC12 • Module SPI (‘Serial Peripheral Interface’): • interface sérielpourpériphériques • types de communications: sérielles synchrones • synchronisation: partage de l’horloge entre les composants qui sont désignés comme maître et esclave, à travers 1 fil supplémentaire • utilisation typique: étendre les capacités du 68HCS12 en interfaçant avec des périphériques synchrones GPA770: Microélectronique appliquée Éric Granger

C.5(2) Sous-systèmes du 68HC12 GPA770: Microélectronique appliquée Éric Granger

Sommaire de la section C.5 C.5 Interfaces sériels de communication du 68HCS12: • Communications sérielles avec microcontrôleurs 2) Sous-systèmes multiples du 68HCS12 • Interface sériel asynchrone – SCI: • caractéristiques du sous-système SCI • registres, programmation et applications • Interface sériel synchrone – SPI: • caractéristiques du sous-système SPI • registres, programmation et applications GPA770: Microélectronique appliquée Éric Granger

C.5(3) Interface sériel asynchrone Caractéristiques du sous-système SCI • Transfert de données: • réalise un lien duplexe – permet d’effectuer une transmission et une réception simultanément • transmission de données – en décalant hors d’un registre à décalage de transfert (via TxD) et en les recevant dans un registre à décalage à réception (via RxD) • les registres de transfert et de réception sont indépendant, et distribués sur 2 registres à 8 bits: SCIDRL et SCIDRH, respectivement GPA770: Microélectronique appliquée Éric Granger

C.5(3) Interface sériel asynchrone Caractéristiques du sous-système SCI • Transfert de données: GPA770: Microélectronique appliquée Éric Granger

C.5(3) Interface sériel asynchrone Caractéristiques du sous-système SCI • Étapes d’un transfert de données TxD→ RxD: (En mode IDLE, TxD = ‘H’) • afin d’initier le transfert, fixer TxD = ‘L’ pour une période de 1 bit – le récepteur détecte alors qu’une transmission est sur le point de commencer • durant la transmission d’un caractère sur TxD • le codage du caractère est en format NRZ • le nombre pré-déterminé de bits par caractère (8 ou 9 bits) est programmable • tous les données sont transférées LSb premier • pour mettre fin au transfert, fixer TxD= ‘H’ pour une période de 1 bit – le récepteur détecte alors a fin GPA770: Microélectronique appliquée Éric Granger

C.5(3) Interface sériel asynchrone Caractéristiques du sous-système SCI GPA770: Microélectronique appliquée Éric Granger

C.5(3) Interface sériel asynchrone Caractéristiques du sous-système SCI • Transmetteur SCI: GPA770: Microélectronique appliquée Éric Granger

C.5(3) Interface sériel asynchrone Caractéristiques du sous-système SCI • Récepteur SCI: GPA770: Microélectronique appliquée Éric Granger

C.5(3) Interface sériel asynchrone Caractéristiques du sous-système SCI • Génération du taux de transfert (Baud): • taux de transfert programmable – par configuration des registres SCIBDH et SCIBDL • le transmetteur et le récepteur du SCI fonctionnent indépendamment, mais selon le même taux de transfert • un compteur modulo à 13 bits dérive le taux ou l’horloge de transfert pour les deux cas GPA770: Microélectronique appliquée Éric Granger

C.5(3) Interface sériel asynchrone Caractéristiques du sous-système SCI • Génération du taux de transfert (Baud): • afin d’alimenter le transmetteur, la fréquence d’horloge de transfertest divisé par 16 • le récepteur à un taux d’acquisition de 16 cycles d’horloge de transfert (échantillons) par temps de bit transmis 1 à 8192 GPA770: Microélectronique appliquée Éric Granger

C.5(3) Interface sériel asynchrone Caractéristiques du sous-système SCI • Détection et vérification de bits: • le récepteur à 16 cycles d’horloge transfert / temps de bit • bit de départ: trois ‘1’ successifs, suivis par des ‘0’ à RT1, 3, 5, 7. Détecte le départ si 2 sur RT3, 5, 7 sont ‘0’, mais drapeau de bruit s’active s’il ne sont pas tous à ‘0’ • bit de donnée (terminaison): vérifie à RT8, 9, 10.Détecte la valeur majoritaire, mais le drapeau de bruit (d’encadrement) s’active s’ils ne sont pas tous identiques GPA770: Microélectronique appliquée Éric Granger

C.5(3) Interface sériel asynchrone Caractéristiques du sous-système SCI • Détection d’erreurs liés à la transmission: • bruit: le récepteur vérifie chaque donné transmise 3 fois pour chaque bit – si le vote majoritaire n’est pas unanime, il y a une erreur de bruit • parité: le récepteur vérifie que le nombre de ‘1’s dans le code est bien paire ou impair – sinon il y a un erreur de parité GPA770: Microélectronique appliquée Éric Granger

C.5(3) Interface sériel asynchrone Caractéristiques du sous-système SCI • Détection d’erreurs liés à la transmission: (suite) • encadrement: si le récepteur détecte le bit de départ, mais pas le bit de terminaison • généralement à cause des différents taux de transfert – probablement due au fait que les 2 horloges n’opèrent pas exactement à la même fréquences • le communication va fonctionner si fclk(transmetteur) est différent de fclk(récepteur) par moins que 4.5% GPA770: Microélectronique appliquée Éric Granger

C.5(3) Interface sériel asynchrone Caractéristiques du sous-système SCI • Capacité de générer des interruptions: • une interruption par SCI, pour indiquer 4 types d’événements: TDRE, TC, RDRF, IDLE (lien inactif) • Réalise 2 techniques de réveil du récepteur: (pour transmissions à 2+ récepteurs) • par reconnaissance de lien inactif: le récepteur se réveil si son fil RxD devient inactif (IDLE) • par démarcation d’adresses: le SCI utilise une adresse reçue dans son SCIDR pendant son sommeille. GPA770: Microélectronique appliquée Éric Granger

C.5(3) Interface sériel asynchrone Registres pertinents du SCI • Chaque sous-système SCI utilise 8 registres: • [$00C8-C9] SCIBDH-L: registres de contrôle du taux de transfert H et L • [$00CA-CB] SCICR1-2: registres de contrôle 1 et 2 • [$00CC-CD] SCISR1-2: registres d’état 1 et 2 • [$00CE-CF] SCIDRH-L: registres de données H et L GPA770: Microélectronique appliquée Éric Granger

C.5(3) Interface sériel asynchrone Registres pertinents du SCI • [$00C8-C9] SCIBDH-L– registres de contrôle du taux transfert H et L: GPA770: Microélectronique appliquée Éric Granger

C.5(3) Interface sériel asynchrone Registres pertinents du SCI • Fixe le taux de transfert selon les bits SBR[12:0]: GPA770: Microélectronique appliquée Éric Granger