A Greatest Common Divisor (GCD) Processor

A Greatest Common Divisor (GCD) Processor. Lecture L5.3. Euclid’s GCD algorithm. GCD(9,15) x = 9 y = 15 y = 15 – 9 = 6 x = 9 – 6 = 3 y = 6 – 3 = 3 GCD(9,15) = 3. 1: int x, y; 2: x = x_input; 3: y = y_input; 4: while (x != y) 5: { 6: if (x<y) 7: y = y-x; 8: else

A Greatest Common Divisor (GCD) Processor

E N D

Presentation Transcript

A Greatest Common Divisor(GCD) Processor Lecture L5.3

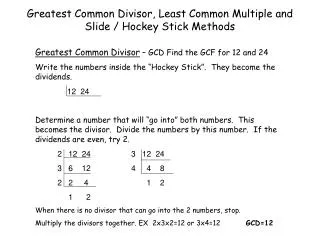

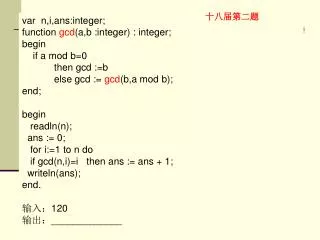

Euclid’s GCD algorithm GCD(9,15) x = 9 y = 15 y = 15 – 9 = 6 x = 9 – 6 = 3 y = 6 – 3 = 3 GCD(9,15) = 3 1: int x, y; 2: x = x_input; 3: y = y_input; 4: while (x != y) 5: { 6: if (x<y) 7: y = y-x; 8: else 9: x = x-y; 10: } 11: output = x;

1: int x, y; 2: x = x_input; 3: y = y_input; 4: while (x != y) 5: { 6: if (x<y) 7: y = y-x; 8: else 9: x = x-y; 10: } 11: output = x;

1: int x, y; 2: x = x_input; 3: y = y_input; 4: while (x != y) 5: { 6: if (x<y) 7: y = y-x; 8: else 9: x = x-y; 10: } 11: output = x;

1: int x, y; 2: x = x_input; 3: y = y_input; 4: while (x != y) 5: { 6: if (x<y) 7: y = y-x; 8: else 9: x = x-y; 10: } 11: output = x;

1: int x, y; 2: x = x_input; 3: y = y_input; 4: while (x != y) 5: { 6: if (x<y) 7: y = y-x; 8: else 9: x = x-y; 10: } 11: output = x;

1: int x, y; 2: x = x_input; 3: y = y_input; 4: while (x != y) 5: { 6: if (x<y) 7: y = y-x; 8: else 9: x = x-y; 10: } 11: output = x;

1: int x, y; 2: x = x_input; 3: y = y_input; 4: while (x != y) 5: { 6: if (x<y) 7: y = y-x; 8: else 9: x = x-y; 10: } 11: output = x;

1: int x, y; 2: x = x_input; 3: y = y_input; 4: while (x != y) 5: { 6: if (x<y) 7: y = y-x; 8: else 9: x = x-y; 10: } 11: output = x;

1: int x, y; 2: x = x_input; 3: y = y_input; 4: while (x != y) 5: { 6: if (x<y) 7: y = y-x; 8: else 9: x = x-y; 10: } 11: output = x;

1: int x, y; 2: x = x_input; 3: y = y_input; 4: while (x != y) 5: { 6: if (x<y) 7: y = y-x; 8: else 9: x = x-y; 10: } 11: output = x;

1: int x, y; 2: x = x_input; 3: y = y_input; 4: while (x != y) 5: { 6: if (x<y) 7: y = y-x; 8: else 9: x = x-y; 10: } 11: output = x;

1: int x, y; 2: x = x_input; 3: y = y_input; 4: while (x != y) 5: { 6: if (x<y) 7: y = y-x; 8: else 9: x = x-y; 10: } 11: output = x;

1: int x, y; 2: x = x_input; 3: y = y_input; 4: while (x != y) 5: { 6: if (x<y) 7: y = y-x; 8: else 9: x = x-y; 10: } 11: output = x;

clr clk clr clk Z GCD Control Unit GCD Datapath C PA PB r0ld r1ld PE wld stld msel(1:0) alusel(2:0) GCD

gcdpath.vhd -- Title: GCD Datapath library IEEE; use IEEE.STD_LOGIC_1164.all; use IEEE.std_logic_unsigned.all; use work.gcd_components.all; entity GCDpath is generic(width:positive); port( PA: in STD_LOGIC_VECTOR (width-1 downto 0); PB: in STD_LOGIC_VECTOR (width-1 downto 0); alusel: b STD_LOGIC_VECTOR (2 downto 0); msel: in STD_LOGIC_VECTOR (1 downto 0); r0ld, r1ld, stld, wld: in STD_LOGIC; clr, clk: in STD_LOGIC; C, Z: out STD_LOGIC; PE: out STD_LOGIC_VECTOR (width-1 downto 0) ); end GCDpath;

a s y gcdpath.vhd (cont.) architecture GCDpath_arch of GCDpath is signal y, a, PEs, PCs, PDs: std_logic_vector(width-1 downto 0); signal s, status: std_logic_vector(3 downto 0); constant bus_width: integer := 4; constant status_width: integer := 4; begin

a s y gcdpath.vhd (cont.) alu1: alu generic map(width => bus_width) port map (a => a, b => PEs, alusel => alusel, status => s, y => y); R0: reg generic map(width => bus_width) port map (d => y, load =>r0ld, clr => clr, clk =>clk, q => PDs); R1: reg generic map(width => bus_width) port map (d => y, load => r1ld, clr => clr, clk =>clk, q => PCs); stat: reg generic map(width => status_width) port map (d => s, load =>stld, clr => clr, clk =>clk, q => status);

a s y gcdpath.vhd (cont.) W: reg generic map(width => bus_width) port map (d => y, load => wld, clr => clr, clk =>clk, q => PEs); M1: mux4g generic map(width => bus_width) port map (a => PA, b => PB, c => PCs, d => PDs, sel => msel, y => a); C <= status(0); Z <= status(2); PE <= PEs; end GCDpath_arch;

clr clk clr clk Z GCD Control Unit GCD Datapath C PA PB r0ld r1ld PE wld stld msel(1:0) alusel(2:0) GCD

1: int x, y; 2: x = x_input; 3: y = y_input; 4: while (x != y) 5: { 6: if (x<y) 7: y = y-x; 8: else 9: x = x-y; 10: } 11: output = x;

VHDLMealy Machine process(present_state, x) init C1 C2 s(t+1) State Register next state s(t) z(t) present state x(t) present input process(present_state, x) clk process(clk, init)

gcd_control.vhd -- Title: GCD Control Unit library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_unsigned.all; entity gcd_control is port ( clr: in STD_LOGIC; clk: in STD_LOGIC; Z: in STD_LOGIC; C: in STD_LOGIC; alusel: out STD_LOGIC_VECTOR (2 downto 0); msel: out STD_LOGIC_VECTOR (1 downto 0); r0ld, r1ld, stld, wld: out STD_LOGIC ); end gcd_control;

gcd_control.vhd (cont.) architecture gcd_control_arch of gcd_control is type state_type is (s0, s1, s2, s3, s4, s5, s6, s7); signal current_state, next_state: state_type; begin statereg: process(clk, clr) -- the state register begin if clr = '1' then current_state <= s0; elsif (clk'event and clk = '1') then current_state <= next_state; end if; end process statereg;

gcd_control.vhd (cont.) C1: process(current_state, Z, C) begin case current_state is when s0 => next_state <= s1; when s1 => next_state <= s2; when s2 => next_state <= s3; when s3 => next_state <= s4; when s4 => if Z = '1' then next_state <= s7; elsif C = '1' then next_state <= s5; else next_state <= s6; end if;

gcd_control.vhd (cont.) when s5 => next_state <= s2; when s6 => next_state <= s2; when s7 => next_state <= s7; end case; end process C1;

a s y gcd_control.vhd (cont.) C2: process(current_state) begin -- Initialize all outputs alusel <= "000"; msel <= "00"; r0ld <= '0'; r1ld <= '0'; stld <= '0'; wld <= '0'; case current_state is when s0 => -- R0 <- x r0ld <= '1' ; r1ld <= '0'; stld <= '1'; wld <= '0'; msel <= "00"; alusel <= "000";

a s y gcd_control.vhd (cont.) when s1 => -- R1 <- Y r0ld <= '0' ; r1ld <= '1'; stld <= '1'; wld <= '0'; msel <= "01"; alusel <= "000"; when s2 => -- W <- R0 r0ld <= '0' ; r1ld <= '0'; stld <= '1'; wld <= '1'; msel <= "11"; alusel <= "000"; when s3 => -- W <- R1 - W r0ld <= '0' ; r1ld <= '0'; stld <= '1'; wld <= '1'; msel <= "10"; alusel <= "010";

a s y gcd_control.vhd (cont.) when s4 => -- W <- R0 r0ld <= '0' ; r1ld <= '0'; stld <= '1'; wld <= '1'; msel <= "11"; alusel <= "000"; when s5 => -- R0 <- W - R1 r0ld <= '1' ; r1ld <= '0'; stld <= '1'; wld <= '0'; msel <= "10"; alusel <= "011"; when s6 => -- R1 <- R1 - W r0ld <= '0' ; r1ld <= '1'; stld <= '1'; wld <= '0'; msel <= "10"; alusel <= "010";

a s y gcd_control.vhd (cont.) when s7 => -- W <- R0 r0ld <= '0' ; r1ld <= '0'; stld <= '1'; wld <= '1'; msel <= "11"; alusel <= "000"; whenothers => null; end case; end process C2; end gcd_control_arch;

clr clk clr clk Z GCD Control Unit GCD Datapath C PA PB r0ld r1ld PE wld stld msel(1:0) alusel(2:0) GCD

GCD.vhd -- Title: Greatest Common Divisor library IEEE; use IEEE.STD_LOGIC_1164.all; use IEEE.std_logic_unsigned.all; use work.GCD_components.all; entity GCD is generic(width:positive); port( PA: in STD_LOGIC_VECTOR ((width-1) downto 0); PB: in STD_LOGIC_VECTOR ((width-1) downto 0); clr, clk: in STD_LOGIC; PE: out STD_LOGIC_VECTOR ((width-1) downto 0) ); end GCD;

GCD.vhd (cont.) architecture GCD_arch of GCD is signal alusel: std_logic_vector(2 downto 0); signal msel: std_logic_vector(1 downto 0); signal C, Z: std_logic; signal r0ld, r1ld, stld, wld: std_logic;

GCD.vhd (cont.) begin U1: gcdpath generic map(width => width) port map (PA => PA, PB => PB, alusel => alusel, msel => msel, r0ld => r0ld, r1ld => r1ld, stld => stld, wld => wld, clr => clr, clk =>clk, PE => PE, C => C, Z => Z); U2: gcd_control port map (alusel => alusel, msel => msel, C => C, Z => Z, r0ld => r0ld, r1ld => r1ld, stld => stld, wld => wld, clr => clr, clk => clk); end GCD_arch;

GCDtest.vhd -- Title: GCD Test library IEEE; use IEEE.STD_LOGIC_1164.all; use IEEE.std_logic_unsigned.all; use work.GCD_components.all; entity GCDtest is port( mclk : in STD_LOGIC; bn : in STD_LOGIC; SW : in STD_LOGIC_VECTOR(1 to 8); led: out std_logic; ldg : out STD_LOGIC; LD : out STD_LOGIC_VECTOR(1 to 8); AtoG : out STD_LOGIC_VECTOR(6 downto 0); A : out STD_LOGIC_VECTOR(3 downto 0) ); end GCDtest;

GCDtest.vhd (cont.) architecture GCDtest_arch of GCDtest is signal r, p: std_logic_vector(15 downto 0); signal clr, clk, cclk, bnbuf: std_logic; signal clkdiv: std_logic_vector(26 downto 0); constant bus_width: positive := 4; begin U00: IBUFG port map (I => bn, O => bnbuf); led <= bnbuf; ldg <= '1'; -- enable 74HC373 latch clr <= bnbuf;

GCDtest.vhd (cont.) -- Divide the master clock (50Mhz) process (mclk) begin if mclk = '1' and mclk'Event then clkdiv <= clkdiv + 1; end if; end process; clk <= clkdiv(0); -- 25 MHz cclk <= clkdiv(17); -- 190 Hz

GCDtest.vhd (cont.) r(15 downto 4) <= "000000000000"; U1: GCD generic map(width => bus_width) port map (PA => SW(1 to 4), PB =>SW(5 to 8), clr => clr, clk =>clk, PE => r(3 downto 0)); U2: binbcd port map (B => r, P => p); U3: x7seg port map (x => p, cclk => cclk, clr => clr, AtoG => AtoG, A => A); LD <= SW; end GCDtest_arch;