Redundant Multi-Level one-hot Residue Number System Based Error Correction Codes

340 likes | 544 Vues

به نام خدا. Redundant Multi-Level one-hot Residue Number System Based Error Correction Codes. Somayyeh Jafarali Jassbi Azad University,Sience and Research Branch September 2009. Outline. VLSI Trends: Moore’s Law Residue Number System Multi-Level Residue Number System

Redundant Multi-Level one-hot Residue Number System Based Error Correction Codes

E N D

Presentation Transcript

به نام خدا Redundant Multi-Level one-hot Residue Number System Based Error Correction Codes Somayyeh Jafarali Jassbi Azad University,Sience and Research Branch September 2009

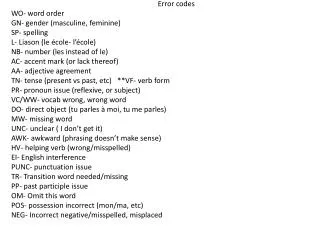

Outline • VLSI Trends: Moore’s Law • Residue Number System • Multi-Level Residue Number System • One-Hot Residue Number System • Redundant Residue Number System • Comparison • References September 2009

Gordon Moore Intel Co-Founder and Chairmain Emeritus Image source: Intel Corporation www.intel.com VLSI Trends: Moore’s Law Moore's Law: The number of transistors incorporated in a chip will approximately double every 24 months. September 2009

History Chinese puzzle, 1500 years ago: What number has the remainders of 2, 3, and 2 when divided by the numbers 7, 5, and 3, respectively? September 2009

FA FA FA FA HA Why RNS? • It is a “inherentlycarry-free” system that performs addition, subtraction, and multiplication as parallel operations. September 2009

Definition The RNS is defined in terms of a set of relatively pair wise prime moduli: September 2009

Definition The dynamic range M is: September 2009

Definition Any integer in the residue class ZM has a unique n-tuple representation given by where xi=X mod mi and is called the ith residue. September 2009

X → x1 x2 X → x1 x2 X → x1 x2 0 → 0 0 5 → 2 0 10 → 1 0 1 → 1 1 6 → 0 1 11 → 2 1 2 → 2 2 7 → 1 2 12 → 0 2 3 → 0 3 8 → 2 3 13 → 1 3 4 → 1 4 9 → 0 4 14 → 2 4 Example September 2009

X X X X X → → → → → x1 x1 x1 x1 x1 x2 x2 x2 x2 x2 x3 x3 x3 x3 x3 36 24 12 48 0 → → → → → 0 0 0 0 0 0 0 0 0 0 3 4 1 2 0 49 25 1 13 37 → → → → → 1 1 1 1 1 1 1 1 1 1 0 2 1 3 4 2 14 38 50 26 → → → → → 2 2 2 2 2 2 2 2 2 2 0 1 3 4 2 3 39 15 51 27 → → → → → 0 0 0 0 0 3 3 3 3 3 1 2 3 0 4 16 52 4 28 40 → → → → → 1 1 1 1 1 0 0 0 0 0 0 4 1 3 2 17 29 5 53 41 → → → → → 2 2 2 2 2 1 1 1 1 1 0 1 4 3 2 6 42 30 54 18 → → → → → 0 0 0 0 0 2 2 2 2 2 3 4 2 0 1 31 7 19 43 55 → → → → → 1 1 1 1 1 3 3 3 3 3 4 0 1 2 3 56 44 8 32 20 → → → → → 2 2 2 2 2 0 0 0 0 0 3 2 1 4 0 57 45 33 21 9 → → → → → 0 0 0 0 0 1 1 1 1 1 4 0 2 1 3 10 46 58 34 22 → → → → → 1 1 1 1 1 2 2 2 2 2 2 3 1 4 0 59 35 47 23 11 → → → → → 2 2 2 2 2 3 3 3 3 3 4 2 1 3 0 Example September 2009

X → x1 x2 X → x1 x2 X → x1 x2 -6 → 0 2 -2 → 1 2 2 → 2 2 -5 → 1 3 -1 → 2 3 3 → 0 3 -4 → 2 0 0 → 0 0 4 → 1 0 -3 → 0 1 1 → 1 1 5 → 2 1 Signed Representation For signed RNS, any integer in (-M/2, M/2] September 2009

Operation September 2009

Operation (Example) September 2009

Operation (Example) September 2009

Operation (Example) September 2009

GeneralArchitecture Binary to RNS RNS Arithmetic RNS to Binary September 2009

Applications • Ad-Hoc Networks • RSA Algorithm • Digital Signal Processing • Digital Filtering • Image Processing • Error Detection and Correction September 2009

Advantages: High-Speed • Carry free • Parallel Operation • Low Power Circuits • Medium Security • Error Detection and Correction Capability • Fault Tolerant September 2009

Multi-Level Residue Number System In Multi-Level RNS we can show each moduli with a smaller and simple moduli in a lower level, it can be two or multi levels September 2009

Multi-Level RNS Converter Therefore the selecting of pair wise prime moduli in big numbers can be easily and the security in a lower layers can be increased September 2009

Multi-Level RNS Converter After doing any operation in lower level we should convert it to higher level and first level September 2009

Multi-Level RNS Advantages • Increase Dynamic Range • Increase Speed of Arithmetic • Increase Security • Simple of moduli selection • Decrease Power consumption September 2009

One-HotRNS moduli remainders are from zero to that in One-Hot representation a signal line is dedicated for each of these numbers and in a second only one line is active September 2009

One-HotRNSAdder Therefore the delay become to 1 transistor and the speed increase massively Barrel shifter Transistor schema September 2009

One-HotRNS Advantages • High-Speed Simple Circuits • Simple and Regular Layout of Arithmetic Circuits • Small of Power Dissipation September 2009

Combination: One-Hot +Multi-level One-Hot Multi-Level RNS Increase Speed Increase Securityof calculate Lower Power Consumption September 2009

RRNS Additional moduli are used in Residue Number System for error detection and correction capability September 2009

RRNS The dynamic range is separated to two domain: legible and illegible September 2009

RRNS In this system with moduli, Number X can represent as follow: September 2009

RRNSAdvantages • Capability of Detection is: r • Capability of Correcting is: • Simultaneous: correcting up to detection up to , if and only if September 2009

Comparison Table (1): comparison RMLONRNS to other RNS s September 2009

References [1] N. S. Szabo and R. I. Tanaka, “Residue Arithmetic and Its Applications to Computer Technology,” New York McGraw-Hill, 1967. [2] B. Parhami, “Computer arithmetic: algorithms and hardware designs.” Oxford, 2001. [3] M. A. Soderstrand and et al. Eds, “Residue number system arithmetic: modern applications in digital signal processing,” New York, IEEE Press, 1986. [4] H. T. How, T. H. Liew, Ee-Lin Kuan, Lie-Liang Yang and Lajos Hanzo, “A Redundant Residue Number System Coded Burst-by-Burst Adaptive Joint-Detection Based CDMA Speech Transceiver,” IEEE Transactions on Vehicular Technology, Vol. 55, No. 1, pp. 387-396, Jan. 2006. [5] F. Barsi and P. Maestrini, “Error Correcting Properties of Redundant Residue Number Systems”, IEEE Transactions on Computers, Vol. C-22 (3), pp. 307-315. Mar. 1973 September 2009

References [6] D. Mandelbaum, “Error Correction in Residue Arithmetic,” IEEE Transactions on Computers, Vol. C-21 (6), pp. 538-545, Jun. 1972. [7] H. Krishna, K.-Y. Lin and J.-D. Sun, “A coding theory approach to error control in redundant residue number systems - Part I: theory and single error correction,” IEEE Transactions on Circuits and Systems, Vol. 39, pp. 8-17, Jan. 1992. [8] J.-D. Sun and H. Krishna, “A coding theory approach to error control in redundant residue number systems -Part II: multiple error detection and correction,” IEEE Transactions on Circuits and Systems, Vol. 39, pp. 18-34, Jan. 1992. [9] H. M. Yassine, “Hierachical Residue number system suitable for VLSI Arithmetic Architectures,” IEEE International Symposium on Circuits and Systems, Vol. 2, pp. 811-814, May 1992. September 2009

Finish Thank you September 2009