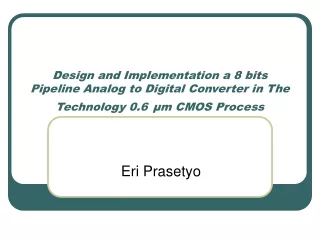

Eri Prasetyo

Design and Implementation a 8 bits Pipeline Analog to Digital Converter in The Technology 0.6 μ m CMOS Process. Eri Prasetyo . Introduction. ADC convert of pixel analogic value to digital value in the image CMOS sensor design. The goal : -ADC can run in the video rate

Eri Prasetyo

E N D

Presentation Transcript

Design and Implementation a 8 bits Pipeline Analog to Digital Converter in The Technology 0.6μm CMOS Process Eri Prasetyo

Introduction • ADC convert of pixel analogic value to digital value in the image CMOS sensor design. • The goal : -ADC can run in the video rate -It must have small size in the layout design • We used the Pipeline ADC because it is simple and it have good conversation rate and good resolution

Architecture Pipelined ADC • One bit per stage Stage 1 Stage 2 V residue V input 2V 3 V 1V 1V 4V 2V 1 0 0 0

Architecture Pipelined ADC • One bit per stage Implemented by Switched Capacitor

Architecture Pipelined ADC • Switched Capacitor • Each stage operates in two phase • Sampling phase • Multiplying phase If D(i) = 1 , Vout(i)=2xVin(i)-Di.Vrefp If D(i) = 0 , Vout(i) = 2xVin(i) – Ďi.Vrefn

Architecture Pipelined ADC • Comparator • Consists of three blocks : • Preamplifier • Decission circuit • Output buffer

Architecture Pipelined ADC • Operational Amplifier • It has a gain 55 dB for bias current 2.5 μA • with Vdd = 5 V and Vss = - 5V

Architecture Pipelined ADC Result of simulation of Operational Amplifier The overall performance of the Op-Amp

Architecture Pipelined ADC • Clock Management • We use latch technique • It is used to hold active condition at multiplying phase until • next stage begin to execute sampling phase • To keep output voltage of residu before conformity at input • next stage

Architecture Pipelined ADC Clock Management The circuit of clock management • Use counter to count some clock to active the address decoder from • each stage • The clock begin working if reset signal • is actived • The clock finish working if reset signal • inactive

Results One stage A/D converter layout Was estimated to occupy about 174 µm X 89 μm

Results 8 bits ADC layout of CHIP photograph

Results Curve linearity of ADC The overall specification And result