The 8086 Assembly Programming Arithmetic and Logical Instructions

The 8086 Assembly Programming Arithmetic and Logical Instructions. Khaled A. Al- Utaibi alutaibi@uoh.edu.sa. Agenda. Introduction Arithmetic Instructions Basic Logical Instructions Shift Instructions Rotate Instructions. Introduction. The arithmetic instructions include: addition,

The 8086 Assembly Programming Arithmetic and Logical Instructions

E N D

Presentation Transcript

The 8086 Assembly ProgrammingArithmetic and Logical Instructions Khaled A. Al-Utaibi alutaibi@uoh.edu.sa

Agenda • Introduction • Arithmetic Instructions • Basic Logical Instructions • Shift Instructions • Rotate Instructions

Introduction • The arithmetic instructions include: • addition, • subtraction, • multiplication, • division, • comparison, • negation, • increment, and • decrement • The logic instructions include: • AND, • OR, • Exclusive-OR, • TEST • NOT, • NEG • shifts, and • rotates

Arithmetic InstructionsAddition • The general format of the ADD instruction is • ADD destination, source • The ADD instruction directs the CPU to add the value contained in the source operand to the value contained in the destination operand and put the result in the destination operand. • All allowed combinations of the two operands are listed below: • Register, Memory (e.g., ADD AX, Var1) • Memory, Register (e.g., ADD Var1, AX) • Register, Register (e.g., ADD AX, BX) • Memory, Immediate (e.g., ADD Var1, 4) • Register, Immediate (e.g., ADD AX, 4) • The result of the addition will affect the flag register according to Figure 1.

Arithmetic InstructionsSubtraction • The general format of the SUB (Subtract) instruction is • SUB destination, source • The SUB instruction directs the CPU to subtract the value contained in the source operand from the value contained in the destination operand and put the result in the destination operand. • All allowed combinations of the two operands are listed below: • Register, Memory (e.g., SUB AX, Var1) • Memory, Register (e.g., SUB Var1, AX) • Register, Register (e.g., SUB AX, BX) • Memory, Immediate (e.g., SUB Var1, 4) • Register, Immediate (e.g., SUB AX, 4) • The result of the subtraction will affect the flag register according to Figure 2.

Figure 2: Carry flags affected by the subtraction instruction.

Arithmetic InstructionsMultiplication • The general format of the MUL (Multiply) instruction is • MUL operand • All allowed operand types are listed below: • Register (e.g., MUL BL) • Memory (e.g., MUL Var1) • The operation of the MUL instruction is as follows: • If the operand in a MUL instruction is 16 bits wide, then it is the multiplier and the AX register is the multiplicand. • The product appears in the DX/AX register pair as shown in Figure 3. • If the operand of a MUL instruction is only 8 bits wide, then it is the multiplier and the AL register is the multiplicand. • The product appears in the AX register as shown in Figure 4. • The result of the multiplication will affect the carry and overflow flags (CF=OF=0 when high section of the result is zero).

Figure 3: 16 bits multiplication. Figure 4: 8 bits multiplication.

Arithmetic InstructionsDivision • The general format of the DIV (Divide) instruction is • DIV operand • All allowed operand types are listed below: • Register (e.g., DIV BL) • Memory (e.g., DIV Var1) • The operation of the DIV instruction is as follows: • If the operand in a DIV instruction is 16 bits wide, the contents of the operand are divided into the DA/AX register pair. • The integer part of the quotient is stored in AX, and the remainder is stored in DX (See Figure 5). • If the operand of a DIV instruction is only 8 bits wide, the contents of the operand are divided into AX. • The integer part of the quotient is stored in AL, and the remainder is stored in AH (See Figure 6). • The result of the division will affect the flags in an unpredictable and therefore are unused.

Figure 5: 16 bits division. Figure 6: 8 bits division.

Arithmetic InstructionsIncrement • The general format of the INC (Increment) instruction is • INC operand • All allowed operand types are listed below: • Register (e.g., INC AL) • Memory (e.g., INC Var1) • This instruction increases the contents of the operand by a value of 1. • Increment instructions affect the flag bits, as do most other arithmetic and logic operations. • The difference is that increment instructions do not affect the carry flag bit. • Carry doesn’t change because we often use increments in programs that depend upon the contents of the carry flag.

Arithmetic InstructionsDecrement • The general format of the DEC(Decrement) instruction is • DEC operand • All allowed operand types are listed below: • Register (e.g., DEC AL) • Memory (e.g., DEC Var1) • This instruction decrement the contents of the operand by a value of 1. • Decrement instructions affect the flag bits, as do most other arithmetic and logic operations. • The difference is that decrement instructions do not affect the carry flag (borrow) bit. • Carry doesn’t change because we often use decrement in programs that depend upon the contents of the carry flag.

Arithmetic InstructionsComparision • The general format of the CMP(Compare) instruction is • CMP destination, source • All allowed operand types are listed below: • Register, Memory (e.g., CMP AX, Var1) • Memory, Register (e.g., CMP Var2, AX) • Register, Register (e.g., CMP AX, BX) • Memory, Immediate (e.g., CMP Var1, 4) • Register, Immediate (e.g., CMP AX, 4) • The CMP instruction accomplishes its task by subtracting the value of the source operand from the value of the destination operand, but it does not store the result into the destination operand. • Instead, it reflects the subtraction effect on the status flags according to Table 1. • Figure 7 Shows how the binary subtraction and status flags logics are implemented.

Table 1: State of the status flags following the execution of a CMP instruction.

Figure 7: Hardware implementation of binary subtraction and status flags logics.

Arithmetic InstructionsComparision • Example 1: show the effect of the instruction CMP AL, BL on the status flags (CF, ZF) assuming that AL and BL contain the following unsigned numbers: • (a) AL = C3H (195 in decimal), BL = C0H (192 in decimal) • (b) AL = C0H (192 in decimal), BL = C3H (195 in decimal) • (c) AL = C3H (195 in decimal), BL = C3H (195 in decimal)

Arithmetic InstructionsComparision • Example 1: show the effect of the instruction CMP AL, BL on the status flags (CF, ZF) assuming that AL and BL contain the following unsigned numbers: • (a) AL = C3H (195 in decimal), BL = C0H (192 in decimal) • C3H – C0H = 11000011 – 11000000 = 00000011 = 03H • CF = 0, ZF = 0 AL > BL • (b) AL = C0H (192 in decimal), BL = C3H (195 in decimal) • C3H – C0H = 11000000 – 11000011 = 11111101 = FDH • CF = 1 (Borrow), ZF = 0 AL < BL • (c) AL = C3H (195 in decimal), BL = C3H (195 in decimal) • C3H – C3H = 11000011 – 11000011 = 00000000 = 00H • CF = 0, ZF = 1 AL = BL

Arithmetic InstructionsComparision • Example 2: show the effect of the instruction CMP AL, BL on the status flags (OF, SF) assuming that AL and BL contain the following signed numbers: • (a) AL = C3H (-61 in decimal), BL = C0H (-64 in decimal) • (b) AL = C0H (-64 in decimal), BL = C3H (-61 in decimal) • (c) AL = C3H (-61 in decimal), BL = 73H (121 in decimal)

Arithmetic InstructionsComparision • Example 2: show the effect of the instruction CMP AL, BL on the status flags (OF, SF) assuming that AL and BL contain the following signed numbers: • (a) AL = C3H (-61 in decimal), BL = C0H (-64 in decimal) • C3H – C0H = 11000011 – 11000000 • = 11000011 + 01000000 • = 00000011 • OF = SF = 0 AL > BL (Note: CF = 0) • (b) AL = C0H (-64 in decimal), BL = C3H (-61 in decimal) • C3H – C0H = 11000000 - 11000011 • = 11000000 +00111101 • = 11111101 • OF = 0 != SF = 1 AL < BL (Note: CF = 1) • (c) AL = C3H (-61 in decimal), BL = 73H (121 in decimal) • C3H – C0H = 11000000 - 01110011 • = 11000000 +10001101 • = 01001101 • OF = 1 != SF = 0 AL < BL (Note: CF = 0)

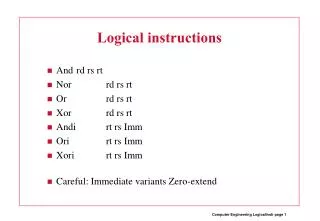

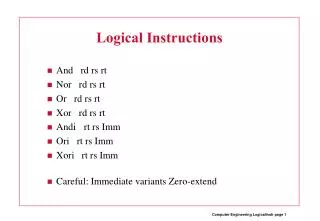

Logical InstructionsAND • The general format of the AND instruction is • AND destination, source • All allowed operand types are listed below: • Register, Memory (e.g., AND AX, Var1) • Memory, Register (e.g., AND Var1, AX) • Register, Register (e.g., AND AX, BX) • Memory, Immediate (e.g., AND Var1, 0FFFFH) • Register, Immediate (e.g., AND AX, 0FFFFH) • Executing an AND instruction performs the traditional Boolean logical AND operation (See Figure 8) bit by bit on destination and source operand and stores the result in the destination operand. • The AND instruction affects the zero flag (ZF), the sign flag (SF), the parity flag (PF) and resets both the carry flag (CF = 0) and overflow flag (OF = 0).

Figure 8: (a) The truth table for the AND operation and (b) the logic symbol of an AND gate.

Logical InstructionsOR • The general format of the OR instruction is • OR destination, source • All allowed operand types are listed below: • Register, Memory (e.g., OR AX, Var1) • Memory, Register (e.g., OR Var1, AX) • Register, Register (e.g., OR AX, BX) • Memory, Immediate (e.g., OR Var1, 0) • Register, Immediate (e.g., OR AX, 0) • Executing an OR instruction performs the traditional Boolean logical OR operation (See Figure 9) bit by bit on destination and source operand and stores the result in the destination operand. • The OR instruction affects the zero flag (ZF), the sign flag (SF), the parity flag (PF) and resets both the carry flag (CF = 0) and overflow flag (OF = 0).

Figure 9: (a) The truth table for the OR operation and (b) the logic symbol of an OR gate.

Logical InstructionsXOR • The general format of the XOR (Exclusive-OR) instruction is • XOR destination, source • All allowed operand types are listed below: • Register, Memory (e.g., XOR AX, Var1) • Memory, Register (e.g., XOR Var1, AX) • Register, Register (e.g., XOR AX, BX) • Memory, Immediate (e.g., XOR Var1, 0FFFFH) • Register, Immediate (e.g., XOR AX, 0FFFFH) • Executing an XOR instruction performs the traditional Boolean logical XOR operation (See Figure 10) bit by bit on destination and source operand and stores the result in the destination operand. • The XOR instruction affects the zero flag (ZF), the sign flag (SF), the parity flag (PF) and resets both the carry flag (CF = 0) and overflow flag (OF = 0).

Figure 10: (a) The truth table for the XOR operation and (b) the logic symbol of an XOR gate.

Logical InstructionsTEST • The general format of the TEST instruction is • TEST destination, source • All allowed operand types are listed below: • Register, Memory (e.g., TEST AX, Var1) • Memory, Register (e.g., TEST Var1, AX) • Register, Register (e.g., TEST AX, BX) • Memory, Immediate (e.g., TEST Var1, 0FFFFH) • Register, Immediate (e.g., TEST AX, 0FFFFH) • The TEST instruction performs the AND operation. • The difference is that the AND instruction changes the destination operand, whereas the TEST instruction does not. • A TEST only affects the condition of the flag register, which indicates the result of the test.

Logical InstructionsNOT • The general format of the NOT instruction is • NOT operand • All allowed operand types are listed below: • Register (e.g., NOT AX) • Memory (e.g., NOT Var1) • The NOT instruction performs the traditional Boolean logical NOT (Inverter)operation (See Figure 11) which complement all bits of its operand (1’s Complement). • The NOT instruction does not affect the flag register.

Figure 11: (a) The truth table for the NOT operation and (b) the logic symbol of an NOT (Inverter) gate.

Logical InstructionsNEG • The general format of the NEG (Negate) instruction is • NEG operand • All allowed operand types are listed below: • Register (e.g., NEG AX) • Memory (e.g., NEG Var1) • The NEG instruction negate its operand (replaces it with its negative, i.e., 2’s Complement). • The NEG instruction does not affect the flag register.

Shift Instructions • Shift instructions position or move numbers to the left or right within a register or memory location. • They also perform simple arithmetic such as multiplication by powers of 2+n(left shift) and division by powers of 2-n(right shift). • The 8086 supports four different shift instructions: Two are logical shifts and two are arithmetic shifts. • All four shift operations appear in Figure 12.

Shift Left Shift Arithmetic Left Shift Right Shift Arithmetic Right Figure 12: The shift instructions showing the operation and direction of the shift.

Shift Instructions • Notice in Figure 10 that there are two right shifts and two left shifts. • The logical shifts move a 0 into the rightmost bit position for a logical left shift and a 0 into the leftmost bit position for a logical right shift. • There are also two arithmetic shifts. • The arithmetic shift left and logical left shift are identical. • The arithmetic right shift and logical right shift are different because the arithmetic right shift copies the sign-bit through the number, whereas the logical right shift copies a 0 through the number.

Shift Instructions • Logical shift operations function with unsigned numbers, and arithmetic shifts function with signed numbers. • Logical shifts multiply or divide unsigned data, and arithmetic shifts multiply or divide signed data. • A shift left always multiplies by 2 for each bit position shifted, and a shift right always divides by 2 for each bit position shifted. • Shifting a number two places, to the left or right, multiplies or divides by 4.

Shift Instructions • The general format of the shift instructions is • XXX destination, count • Where: • XXX is the shift mnemonic (i.e., SHL, SHR, SAL, SAR), • destination is a general-purpose register or memory reference, and • count is either 1 or CL register • Examples: • SHL AX, 1 • SHL AX, CL

Rotate Instructions • Rotate instructions position binary data by rotating the information in a register or memory location, either from one end to another or through the carry flag. • The four available rotate instructions appear in Figure 13. • Numbers rotate through a register or memory location, through the C flag (carry), or through a register or memory location only. • With either type of rotate instruction, the programmer can select either a left or a right rotate.

Shift Left Shift Arithmetic Left Shift Right Shift Arithmetic Right Figure 13: The rotate Target register or memory instructions showing the direction and operation of each rotate.

Rotate Instructions • The general format of the shift instructions is • XXX destination, count • Where: • XXX is the rotate mnemonic (i.e., ROCL, ROCR, ROL, ROR), • destination is a general-purpose register or memory reference, and • count is either 1 or CL register • Examples: • ROL AX, 1 • ROL AX, CL