Delayed Branching Explained

This document explores the concept of delayed branching in deeply pipelined processors, particularly focusing on static branch policies and their impact. It describes how target addresses are calculated and branches resolved within a pipeline structure, and compares various handling techniques like always flush, predict taken, and predict not taken strategies. The study uses MIPS architecture to demonstrate normal branch behavior in an array copy program. The insights provided aim to clarify the performance implications of static branch handling mechanisms in processor design.

Delayed Branching Explained

E N D

Presentation Transcript

Delayed Branching Explained Winter, 2005 Print a copy of these and handout, not the old one

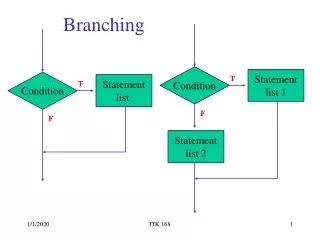

Chapter Example: Impact of Basic Static Branch Policies in Deeply Pipelined Processors Notes: Assume that Target Address is calculated at the end of 3rd stage and Branches are resolved at the end of 4th stage. Pipeline Stage: Since the processor has deeper pipeline We can name first few stages factitiously asIF, ID, TA (Target Address Calc), BC (Branch Condition Evaluation), etc

Exercise A3 Pipeline Example:Notes: Target Address is calculated at the end of ID stage and Branches are resolved at the end of EXE stage. Assumption: Processor has no static branch penalty reduction technique, e.g, Delayed branching, Predict Taken, etc. Note that the processor has a strategy to stall until BC is executed

Study of MIPS 5-stage Integer Pipeline: Simple Array Copy program

MIPS AGGRESSIVE BRANCHING CASE (Normal Behavior of Branch in Array Copy Program)

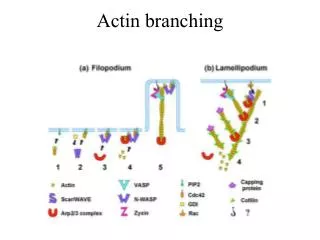

Delayed Branching: Since there is always an instruction between the target and branch, hence delay.

Cancelled Branching: Instruction in delay slot NOT executed if branch is not taken (MIPS BEQL (Branch if Equal Likely is an Example)