Non Redundant Data Cache

ISLPED´03, Seoul (Korea) - August 25-27, 2003. Non Redundant Data Cache. Carlos Molina, Carles Aliagas and Montse García Universitat Rovira i Virgili – Tarragona, Spain {cmolina,caliagas,mgarciaf}@etse.urv.es Antonio González and Jordi Tubella

Non Redundant Data Cache

E N D

Presentation Transcript

ISLPED´03, Seoul (Korea) - August 25-27, 2003 Non Redundant Data Cache Carlos Molina, Carles Aliagas and Montse García Universitat Rovira i Virgili – Tarragona, Spain{cmolina,caliagas,mgarciaf}@etse.urv.es Antonio González and Jordi Tubella Universitat Politècnica de Catalunya – Barcelona, Spain {antonio,jordit}@ac.upc.es

Motivation • Caches spend close to 50% of total die area • Caches may be responsible for 10% to 20% of total power dissipated by a processor

Objective • To reduce die area • But mantaining miss ratio • Latency • Energy consumption

Value A 12345 Tag X Value B 12345 Tag Y Conventional Cache • If (Value A==Value B) then Value Redundancy

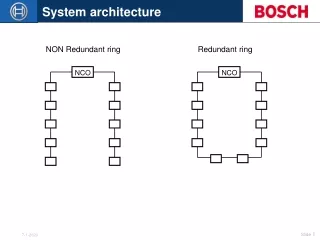

12345 count 12345 Tag X Tag X 12345 12345 Tag Y Tag Y Die Area Reduction Additional Hardware: Pointers Additional Hardware: Counters Non Redundant Data Cache (1) Pointer Table Value Table

Data Value Inlining • Some values can be represented with a small number of bits (Narrow Values) • Narrow values can be inlined into pointer area • Simple sign extension is applied • Benefits • enlarges logical capacity of VT • reduces latency • reduces power dissipation

10 count count Tag X Tag X Tag Y Tag Y 10 10 Non Redundant Data Cache (2) Pointer Table Value Table

Simulation Enviroment • Simulators • Cacti tool version 3.0 (Static Analysis) • Alpha version of SimpleScalar 3.0 (Dynamic Analysis) • Benchmarks • Spec2000 • Maximum Optimization Level • DEC C & F77 compilers with -non_shared -O5 • Statistics Collected for 1 billion instructions • Skipping initializations

Miss Rate vs Die Area % % % % Miss Ratio % % % % | | | 0,1 0,5 1,0 cm2

Results • Caches ranging from 256 KB to 4 MB

Conclusions • High degree of value replication is present in conventional caches • Non redundant data cache • Data value inlining • Die area reduction • Energy consumption reduction • Access time reduction • Minor miss ratio increasing

ISLPED´03, Seoul (Korea) - August 25-27, 2003 Non Redundant Data Cache Carlos Molina, Carles Aliagas and Montse García Universitat Rovira i Virgili – Tarragona, Spain{cmolina,caliagas,mgarciaf}@etse.urv.es Antonio González and Jordi Tubella Universitat Politècnica de Catalunya – Barcelona, Spain {antonio,jordit}@ac.upc.es