Time-Interleaved Continuous-Time Delta-Sigma Modulators

Time-Interleaved Continuous-Time Delta-Sigma Modulators. by Trevor C. Caldwell Supervisor: Prof. David A. Johns June 24 th , 2005 Ph.D. Candidate Graduate Department of Electrical and Computer Engineering, Electronics Group University of Toronto. Introduction.

Time-Interleaved Continuous-Time Delta-Sigma Modulators

E N D

Presentation Transcript

Time-Interleaved Continuous-Time Delta-Sigma Modulators by Trevor C. Caldwell Supervisor: Prof. David A. Johns June 24th, 2005 Ph.D. Candidate Graduate Department of Electrical and Computer Engineering, Electronics Group University of Toronto

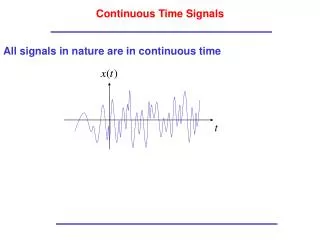

Introduction • DS modulators popular for A/D conversion • Bandwidth limited by OSR, max sampling frequency • Goal: Increase bandwidth of DS modulator • Time-interleaving for a DT DS modulator • Use Block Digital Filtering [Poorfard, 97] • 1 filter becomes M filters operating at 1/M of fsampling • Requires M integrators, ADCs, DACs operating at 1/M of fsampling • CT DS modulator • Operate faster than DT DS modulators • Inherent anti-aliasing filter

CT Time-Interleaved DS Modulator • Continuous-Time equivalent of DTTI modulator • Time-Interleaved by 2, Continuous-Time, 3rd-order • Single path of integrators remains (half as many as expected) • Requires low-latency critical path

CT Time-Interleaved DS Modulator • Test Results (1.8V, 0.18um CMOS): • Sampling Frequency = 100MHz/200MHz, OSR=5 • Input Bandwidth = 10MHz/20MHz • SNDR = 57dB/49dB • Power = 101mW/103mW

High-Speed CTTI DS Modulator • High-Speed Improvements • Reduce latency requirements of critical path • Increase tolerance to non-idealities (jitter, opamp bandwidth) • Add extra DAC feedback paths, NRZ DACs • Future Work: • Implement new modulator with similar resolution, increased bandwidth