SPI&UART

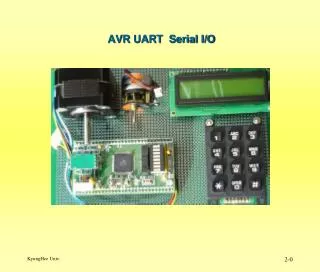

SPI&UART. SPI : Serial Peripheral Interface Bus. 控制方式:. Master. Slave. Serial Clock. 连接方式. SPI 原理框图. 时钟时序:. 高低电平位. 时钟相位. 最高有效位. 读写原理:. MOSI. 发送缓冲器. 发送缓冲器. 移位寄存器. 移位寄存器. MISO. 接收缓冲器. 接收缓冲器. Slave. Master. UART: Universal Asynchronous Receiver/Transmitter. 串行控制寄存器.

SPI&UART

E N D

Presentation Transcript

SPI: Serial Peripheral Interface Bus • 控制方式: Master Slave Serial Clock • 连接方式

时钟时序: 高低电平位 时钟相位 最高有效位

读写原理: MOSI 发送缓冲器 发送缓冲器 移位寄存器 移位寄存器 MISO 接收缓冲器 接收缓冲器 Slave Master

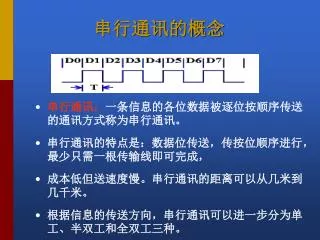

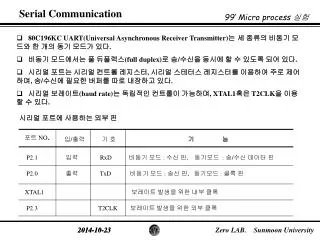

UART:Universal Asynchronous Receiver/Transmitter 串行控制寄存器 同一个SBUF0地址可以访问发送寄存器和接收寄存器。写SBUF0时自动访问发送寄存器;读SBUF0时自动访问接收寄存器,不可能从发送数据寄存器中读数据。 接收到数据字节RI0位被置‘1’ 发送完成TI0位被置‘1’

工作方式 UART0控制寄存器 8位 UART 方式,每个数据字节共使用 10 位:一个起始位、8 个数据位(LSB 在先) 和一个停止位。数据从 TX0 引脚发送,在 RX0 引脚接收。在接收时,8 个数据位存入 SBUF0, 停止位进入 RB80(SCON0.2)。 最低有效位 第9接收位 9位UART方式,每个数据字节共使用11位:一个起始位、8个数据位(LSB在先)、一个可编程的第九位和一个停止位。第九发送数据位由TB80(SCON0.3)中的值决定,由用户软件赋值。它可以被赋值为PSW中的奇偶位P(用于错误检测),或用于多处理器通信。在接收时,第九数据位进入RB80(SCON0.2),停止位被忽略。

详细说明8位方式: • 当软件向SBUF0寄存器写入一个字节时开始数据发送。在发送结束时(停止位开始)发送中断标志TI0(SCON0.1)被置‘1’。在接收允许位REN0(SCON0.4)被置‘1’后,数据接收可以在任何时刻开始。收到停止位后,如果满足下述条件则数据字节将被装入到接收寄存器SBUF0:RI0必须为逻辑‘0’;如果MCE0为逻辑‘1’,则停止位必须为‘1’。在发生接收数据溢出的情况下,先接收到的8位数据被锁存到SBUF0,而后面的溢出数据被丢弃。 • 如果这些条件满足,则8位数据被存入SBUF0,停止位被存入RB80,RI0标志被置位。如果这些条件不满足,则不装入SBUF0和RB80,RI0标志也不会被置‘1’。如果中断被允许,在TI0或RI0置位时将产生一个中断 多处理器通信允许